In the world of portable electronics, e-readers stand out for their incredible battery life, often lasting weeks on a single charge. A key factor behind this efficiency is the PCB stackup design, which plays a critical role in managing power consumption. If you're looking to design an e-reader with optimized battery life, focusing on the E-Reader PCB layer stack, low power PCB design, and battery optimization PCB strategies is essential. In this comprehensive guide, we’ll walk you through the best practices for designing a PCB stackup that minimizes E-Ink power consumption and maximizes efficiency using the right PCB material for battery life.

Let’s dive into the details of how a well-thought-out PCB stackup can make a significant difference in e-reader performance, ensuring longer battery life without sacrificing functionality.

Why PCB Stackup Design Matters for E-Reader Battery Life

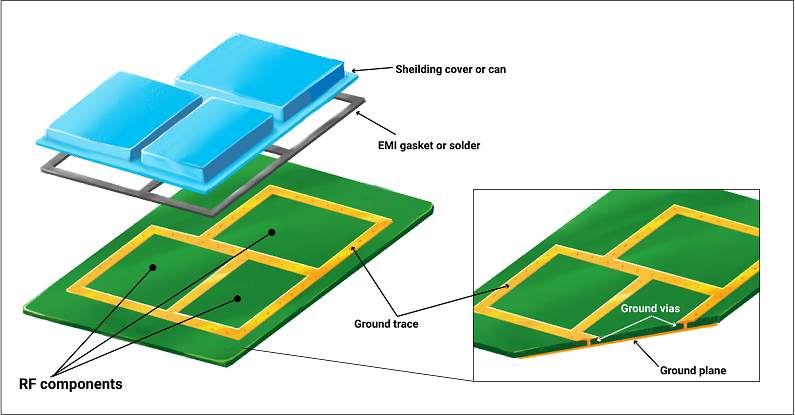

The printed circuit board (PCB) stackup refers to the arrangement of copper layers and insulating materials that form the foundation of any electronic device. For e-readers, where battery life is a top priority, the stackup design directly impacts power efficiency. A poorly designed stackup can lead to energy losses through heat, electromagnetic interference (EMI), or inefficient signal routing, all of which drain the battery faster.

By optimizing the E-Reader PCB layer stack, you can reduce power consumption in several ways, such as minimizing signal noise, improving grounding, and selecting materials that support low power operation. Since e-readers primarily use E-Ink displays, which are inherently low-power compared to LCDs, the PCB design must complement this advantage by ensuring minimal energy waste elsewhere in the system.

Key Principles of Low Power PCB Design for E-Readers

Designing a PCB for low power consumption requires careful attention to several factors. Below, we outline the core principles that guide low power PCB design specifically for e-readers.

1. Minimize Layer Count for Simplicity and Efficiency

While multi-layer PCBs are common in complex devices, e-readers often don’t require an extensive number of layers due to their relatively simple circuitry. A 4-layer or 6-layer PCB is often sufficient for most e-reader designs. Reducing the number of layers not only lowers manufacturing costs but also decreases parasitic capacitance and inductance, which can contribute to power loss. For example, a 4-layer stackup might include two signal layers, a ground plane, and a power plane, providing a balance between functionality and efficiency.

2. Prioritize Ground Planes for Noise Reduction

A solid ground plane is essential for minimizing EMI, which can interfere with the low-power operation of E-Ink displays. Place a dedicated ground plane adjacent to signal layers to provide a low-impedance return path for currents. This reduces noise and prevents unnecessary power draw caused by signal interference. For instance, in a 4-layer stackup, ensure the ground plane is on layer 2 or 3, directly beneath the top signal layer.

3. Optimize Power Distribution Network (PDN)

The power distribution network in an e-reader PCB must deliver stable voltage with minimal losses. Use wide power traces or dedicated power planes to reduce resistance and prevent voltage drops. Additionally, place decoupling capacitors close to power-hungry components like the processor or Wi-Fi module to stabilize voltage and reduce power spikes that could drain the battery. A typical target impedance for a PDN in low-power devices might be around 0.1 ohms to ensure minimal energy loss.

Choosing the Right PCB Material for Battery Life

The choice of PCB material for battery life is another critical aspect of e-reader design. Materials impact not just the structural integrity of the board but also its electrical properties, which directly affect power efficiency.

1. Low Dielectric Constant Materials

Materials with a low dielectric constant (Dk) help reduce signal loss and power consumption, especially in high-frequency areas like Wi-Fi or Bluetooth modules. For e-readers, consider using FR-4 with a Dk of around 4.2-4.5 for cost-effective designs, or opt for advanced materials like Rogers laminates with a Dk closer to 3.0 for premium devices where efficiency is paramount. Lower Dk values minimize capacitance between layers, reducing energy waste.

2. Thin Dielectric Layers for Compact Design

Using thinner dielectric layers between copper layers can reduce the overall board thickness, which is ideal for slim e-reader designs. However, thinner layers also mean lower parasitic capacitance, which can help in battery optimization PCB strategies by reducing power loss. A typical dielectric thickness for low-power designs might range from 0.1 mm to 0.2 mm, balancing compactness with manufacturability.

3. Thermal Management with Material Selection

Heat dissipation is a concern even in low-power devices like e-readers. Excess heat can degrade battery performance over time. Choose materials with good thermal conductivity to dissipate heat effectively. Adding thermal vias near heat-generating components can also help transfer heat away from the battery, preserving its lifespan.

Reducing E-Ink Power Consumption Through PCB Design

E-Ink displays are a hallmark of e-readers, known for their ultra-low power usage since they only draw power when the screen content changes. However, the PCB design must support this efficiency by minimizing E-Ink power consumption through careful layout and component selection.

1. Optimize Driver Circuit Layout

The E-Ink display driver circuit should be placed close to the display connector to minimize signal trace length. Long traces can introduce resistance and capacitance, leading to higher power draw during screen refreshes. Keep trace lengths under 50 mm if possible, and use a ground plane beneath these traces to reduce noise.

2. Use Low-Power Components

Select microcontrollers (MCUs) and power management ICs (PMICs) specifically designed for low-power operation. For example, an MCU with a deep sleep mode consuming less than 1 μA can significantly reduce overall power usage when the e-reader is idle. Pair this with a PMIC that offers high efficiency (above 90%) at low load conditions to prevent unnecessary battery drain.

3. Manage Refresh Rates

While not strictly a PCB design factor, the firmware controlling the E-Ink display refresh rate can be supported by the hardware design. Ensure the PCB layout allows for clean signal transmission to avoid refresh errors, which could force unnecessary redraws and increase power consumption. A refresh rate of 1 Hz or lower for static content can keep power usage minimal.

Advanced Stackup Techniques for Battery Optimization

For engineers looking to push the boundaries of battery optimization PCB design, advanced stackup techniques can provide additional gains in efficiency.

1. Split Power Planes for Zoning

In a multi-layer PCB, split the power plane into zones for different components, such as the E-Ink display, processor, and wireless modules. This prevents high-power components from interfering with low-power sections, reducing overall energy waste. For instance, a 6-layer stackup might dedicate layer 4 as a split power plane with separate zones maintaining isolation through careful routing.

2. Control Impedance for Signal Integrity

Impedance mismatches in signal traces can lead to reflections, requiring more power to maintain signal integrity. Design critical traces, such as those for the E-Ink driver, with controlled impedance—typically targeting 50 ohms for single-ended signals. Use PCB design software to calculate trace width and spacing based on the dielectric constant of your chosen material.

3. Minimize Via Usage

Vias introduce inductance and resistance, which can lead to small but cumulative power losses. Plan your stackup to reduce the need for vias by routing signals on adjacent layers whenever possible. When vias are necessary, use microvias for smaller footprints and lower parasitic effects in high-density areas.

Testing and Validation for Power Efficiency

Once your PCB stackup is designed, testing is crucial to validate its performance in terms of power efficiency. Use a multimeter or power analyzer to measure current draw during different operating modes, such as idle, screen refresh, and wireless activity. Target a standby current of under 10 μA for optimal battery life. Additionally, perform thermal imaging to identify hotspots that could indicate inefficient power distribution or material issues.

Simulate real-world usage by cycling the e-reader through typical tasks like page turns and downloads over several hours. Compare the measured battery drain against your design goals, tweaking the stackup or component placement as needed to meet targets.

Conclusion: Building the Future of Efficient E-Readers

Designing an e-reader with exceptional battery life starts with a carefully planned PCB stackup. By focusing on a streamlined E-Reader PCB layer stack, adopting low power PCB design principles, and selecting the right PCB material for battery life, you can create a device that maximizes efficiency. From reducing E-Ink power consumption to implementing advanced battery optimization PCB techniques, every detail counts in achieving weeks-long battery performance.

With these strategies in hand, you’re equipped to tackle the challenges of e-reader PCB design, delivering a product that stands out for its endurance and user satisfaction. Keep iterating, testing, and refining your approach to stay ahead in the ever-evolving world of portable electronics.

ALLPCB

ALLPCB