Introduction

Modern electronics demand ever-higher component densities and faster signal speeds, pushing printed circuit board designers toward advanced interconnect technologies. Sequential build-up PCBs represent a cornerstone of high-density interconnect solutions, enabling compact designs for applications like smartphones, medical devices, and automotive systems. At the heart of this process lie microvias, which provide precise vertical interconnections between layers while minimizing board real estate. These small vias, typically formed by laser drilling, allow for multilayer stacking without the space penalties of traditional through-holes. By integrating microvias effectively, engineers achieve superior routing density, reduced signal path lengths, and improved electrical performance. This article explores the critical role of microvias in sequential build-up processes, focusing on design, fabrication, filling, and reliability to guide electric engineers in optimizing their PCB layouts.

Understanding Sequential Build-Up PCBs and Microvias

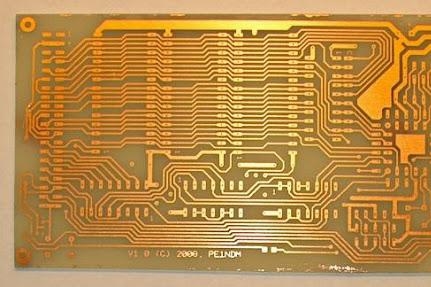

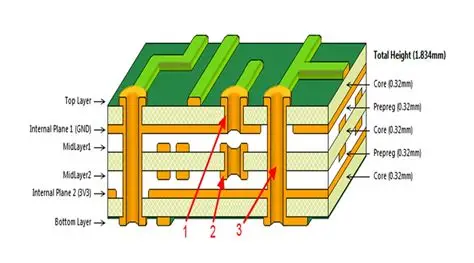

Sequential build-up, often abbreviated as SBU, involves constructing high-density interconnect boards by incrementally adding thin dielectric layers and copper foils around a central core. Unlike all-at-once lamination, this method permits the formation of blind and buried vias at each build-up cycle, maximizing interlayer connections. Microvias serve as the primary interconnects in SBU, linking adjacent layers with minimal diameter and depth to support fine-pitch components. Their implementation enables HDI structures classified into types such as passive, active, or embedded components, as outlined in industry design guidelines. Engineers benefit from shorter signal paths that reduce inductance and crosstalk, enhancing overall board performance. This layered approach directly addresses the challenges of miniaturization in high-performance electronics.

The relevance of microvias in SBU stems from the need to accommodate ball grid arrays and chip-scale packages with pitches below standard through-hole capabilities. Without microvias, achieving the required density would demand thicker boards or wider traces, compromising thermal management and signal integrity. In practice, SBU with microvias supports via-in-pad configurations, freeing surface area for components. Factory processes align these features with qualification specifications to ensure consistency across production runs. As board complexity grows, microvias become indispensable for maintaining electrical continuity while adhering to manufacturability constraints.

Microvia Design Sequential Build-Up: Key Engineering Principles

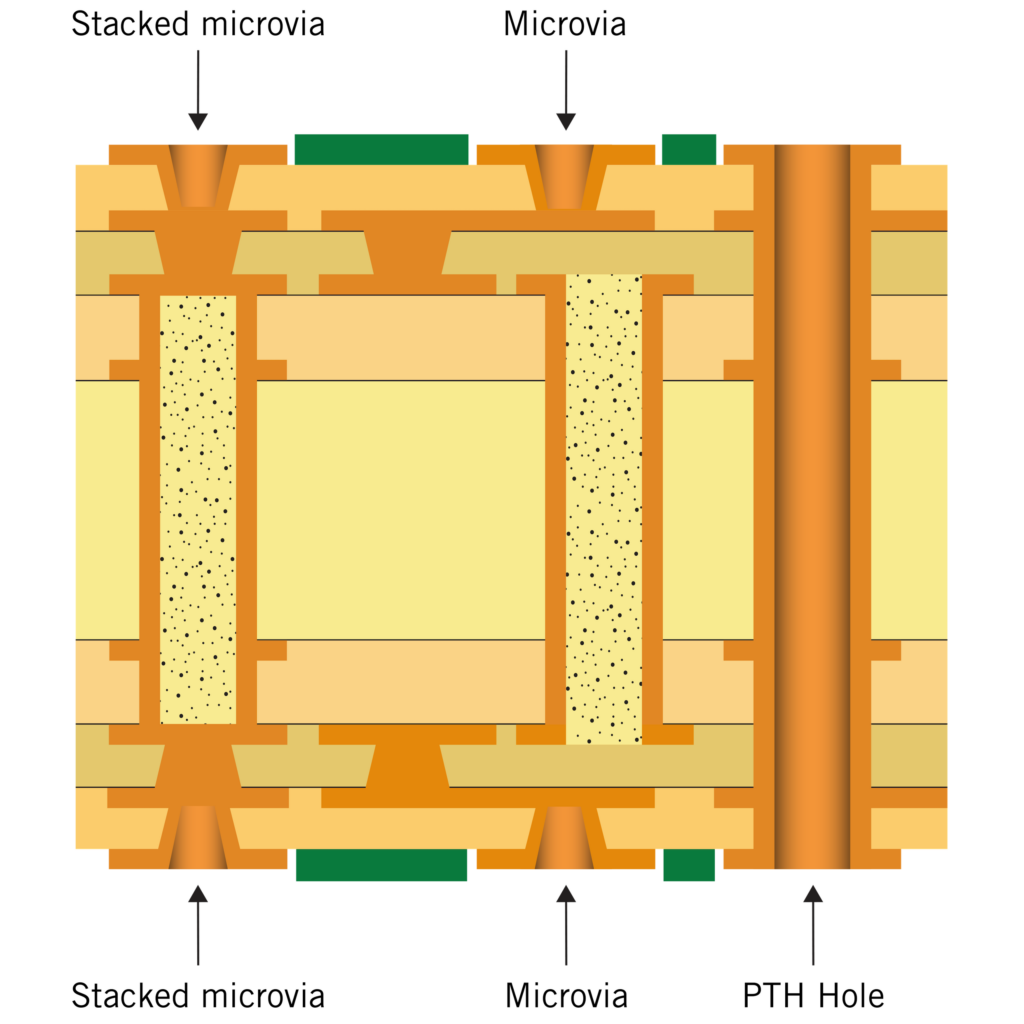

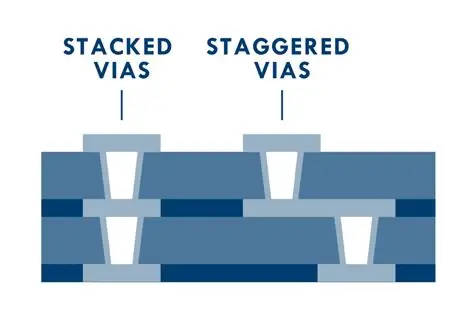

Microvia design sequential build-up requires careful planning of via placement, size, and configuration to balance density with manufacturability. Engineers must consider stacked versus staggered arrangements, where stacked microvias align directly atop one another for deeper connections, while staggered ones offset to distribute stress. The IPC-2226A standard provides sectional guidelines for HDI features, emphasizing aspect ratios and land geometries that prevent drilling inaccuracies. Design rules account for dielectric thickness, ensuring laser energy penetrates cleanly without residue buildup. Signal integrity analysis during layout verifies impedance control around microvia transitions. These principles enable engineers to maximize routing channels without sacrificing reliability.

In microvia design sequential build-up, pad size and annular ring dimensions play a pivotal role in plating uniformity and thermal expansion matching. Staggered vias reduce cumulative drill depth, mitigating taper effects common in deeper structures. Engineers simulate thermomechanical stresses to predict failure modes like cracking under reflow cycles. Compliance with HDI stackup types ensures compatibility with sequential lamination cycles. By optimizing fanout from BGAs, designs achieve higher escape routing efficiency. This structured approach aligns fabrication capabilities with performance targets.

Microvia Fabrication Sequential Build-Up: Process Fundamentals

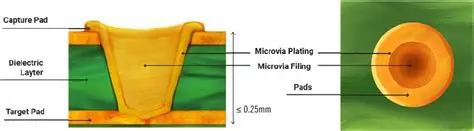

Microvia fabrication sequential build-up begins with precise laser ablation of dielectric material to form blind vias. UV lasers excel for resin-based dielectrics due to their short wavelength, achieving clean sidewalls, while CO2 lasers suit glass-reinforced materials. Post-drilling desmear removes smear and debris, preparing surfaces for metallization. Sequential cycles repeat this for each build-up layer, with intermediate lamination bonding new foils. Plasma treatment enhances adhesion before plating. These steps ensure void-free structures critical for high-speed applications.

During fabrication, engineers monitor via profile to avoid hourglassing or necking, which compromise conductivity. Electrolytic copper plating deposits conformal layers inside vias, followed by surface planarization via chemical mechanical polishing. For complex stackups, intermediate inspections verify geometry per performance specifications like IPC-6012F. Sequential processing demands tight control over registration to align vias across layers. Variations in material CTE influence via integrity during lamination. Mastering these techniques yields robust interconnects for demanding environments.

Microvia Filling Sequential Build-Up: Techniques and Considerations

Microvia filling sequential build-up employs electroplating or conductive paste to create solid conductors, eliminating voids that could trap contaminants. Copper electroplating fills vias bottom-up, leveraging additives for uniform deposition and minimal dimpling. This method supports high-current densities, ideal for stacked configurations requiring multiple reflows. Conductive pastes, filled with silver or copper particles, offer an alternative for cost-sensitive designs, applied via screen printing before lamination. Post-fill inspection confirms complete fill per acceptability criteria. These approaches enhance thermal dissipation and mechanical strength.

In microvia filling sequential build-up, plating parameters like current density and bath chemistry directly impact reliability. Overplating risks dome formation, complicating surface finishes, while underfill leads to electromigration risks. Engineers select fills based on via depth and board class, ensuring compatibility with subsequent processes. IPC-A-600K guidelines define acceptable fill characteristics, such as no cracks or separations. Hybrid methods combine plating with paste for ultra-fine vias. Optimized filling sustains performance under operational stresses.

Microvia Reliability Sequential Build-Up: Critical Factors

Microvia reliability sequential build-up hinges on mitigating thermomechanical stresses from CTE mismatches between copper and dielectrics. Thermal cycling induces shear at via interfaces, potentially causing opens or high resistance. Conductive anodic filamentation poses another risk in humid environments, propagating along fiber paths. Reliability testing simulates field conditions, including multiple reflows and powered cycling. Adhering to IPC-6012F qualification ensures boards withstand assembly and operation. Engineers prioritize low-loss dielectrics with matched coefficients for long-term stability.

Stacked microvias amplify reliability challenges due to compounded stresses, necessitating staggered alternatives where possible. Fill quality directly correlates with fatigue life, as voids accelerate crack propagation. IPC-2226A recommends design margins for via-in-pad and escape patterns to distribute loads. Accelerated life testing reveals weaknesses early, guiding material selections. Board warpage control during lamination preserves via alignment. These factors collectively determine field performance in high-reliability sectors.

Best Practices for Implementing Microvias in Sequential Build-Up

Engineers should start with stackup planning, defining microvia orders early to minimize lamination cycles. Select laser-drillable resins with low Z-axis CTE for reduced stress. Maintain conservative aspect ratios per IPC-2226A to facilitate plating. Incorporate filled vias under components to support fine-pitch escapes. Simulate signal integrity and power delivery around microvias. Collaborate with fabricators on DFM reviews to refine designs.

During fabrication, implement inline metrology for via dimensions and fill verification. Use carrier panels for thin cores to prevent handling damage. Optimize desmear chemistries for residue-free vias. For reliability, conduct Weibull analysis on test coupons mimicking production stackups. Monitor process windows tightly across cycles. These practices yield high first-pass yields and robust products.

Conclusion

Microvias fundamentally enhance sequential build-up PCBs by enabling unprecedented density and performance gains. From precise design and fabrication to reliable filling, each stage demands engineering rigor aligned with standards like IPC-2226A and IPC-6012F. Electric engineers leveraging these principles achieve compact, high-speed boards suited for next-generation electronics. Prioritizing reliability through structured processes ensures longevity in demanding applications. As interconnect demands evolve, microvia technologies will continue driving innovation in PCB engineering.

FAQs

Q1: What key aspects define microvia design sequential build-up?

A1: Microvia design sequential build-up focuses on configuring stacked or staggered vias within HDI stackups to optimize density. Engineers follow IPC-2226A for aspect ratios, land sizes, and placement rules that ensure manufacturability. Staggered arrangements reduce stress concentration, while fanout strategies support BGA escapes. This approach minimizes signal path lengths and enhances routing efficiency in multilayer boards.

Q2: How is microvia fabrication sequential build-up performed?

A2: Microvia fabrication sequential build-up uses laser drilling followed by desmear and plating in iterative cycles around a core. UV or CO2 lasers create precise blind vias, with plasma cleaning improving adhesion. Electrolytic plating builds conductive paths, planarized for subsequent layers. Process controls per IPC-6012F verify geometry and integrity. This method supports complex HDI structures reliably.

Q3: What factors influence microvia reliability sequential build-up?

A3: Microvia reliability sequential build-up depends on CTE matching, fill quality, and stress distribution to prevent cracking or CAF. Thermal cycling tests simulate reflow stresses, with staggered vias outperforming stacked in fatigue. IPC-6012F qualifications guide performance metrics. Low-loss materials and conservative designs extend life cycles. Monitoring warpage during lamination preserves alignment.

Q4: What are common methods for microvia filling sequential build-up?

A4: Microvia filling sequential build-up primarily uses copper electroplating for solid, high-conductivity fills or conductive pastes for simpler processes. Plating employs bottom-up deposition with additives to avoid voids, while pastes suit shallow vias via printing. IPC-A-600K defines acceptability for no separations. Selection balances cost, depth, and reflow tolerance. Complete fills boost thermal and mechanical performance.

References

IPC-2226A - Sectional Design Standard for High Density Interconnect (HDI) Printed Boards. IPC, 2017

IPC-6012F - Qualification and Performance Specification for Rigid Printed Boards. IPC, 2023

IPC-A-600K - Acceptability of Printed Boards. IPC, 2020

ALLPCB

ALLPCB