Introduction

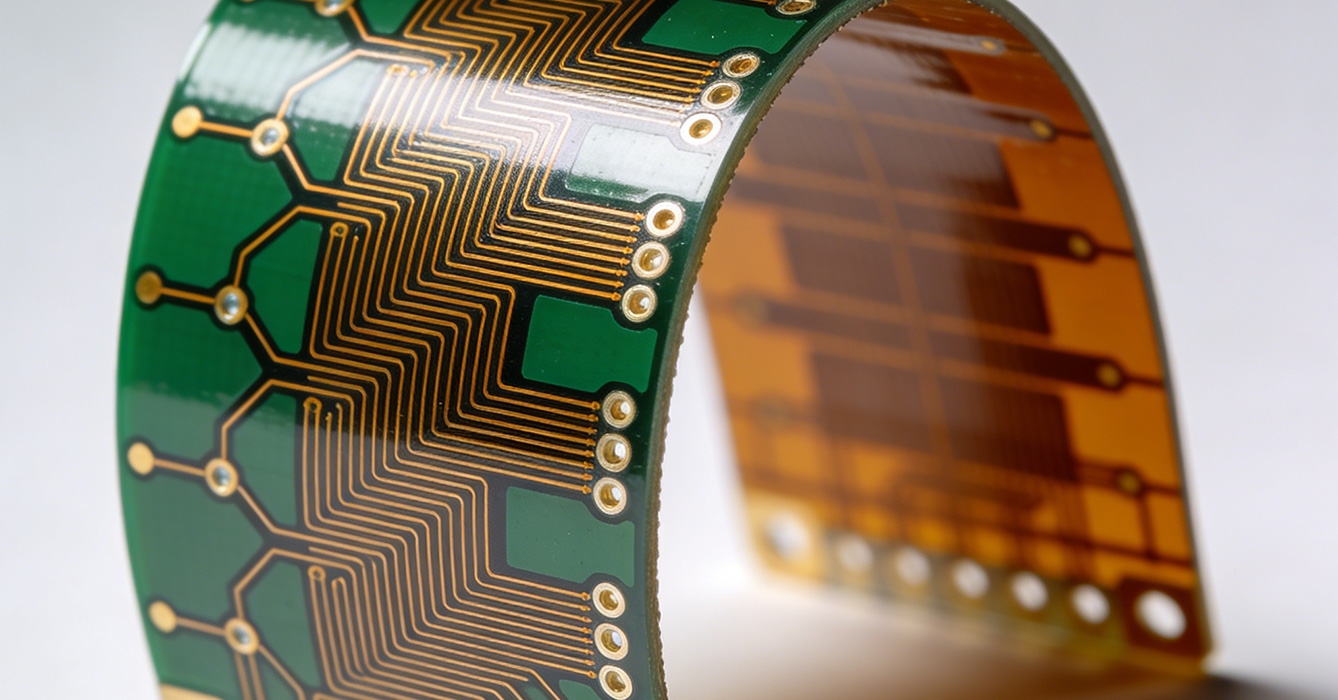

In modern PCB layout, achieving high density while maintaining superior PCB performance demands precise microvia placement. Microvias enable compact interconnects in high-density interconnect boards, supporting advanced applications like smartphones and medical devices. Proper microvia placement directly impacts signal integrity, reducing losses and crosstalk in high-speed designs. Engineers must balance density with reliability, considering factors like thermal expansion and plating quality. This article explores strategies for via optimization, drawing on established engineering principles to guide PCB designers toward optimal outcomes. By mastering these techniques, teams can enhance overall PCB performance without compromising manufacturability.

What Are Microvias and Why Microvia Placement Matters

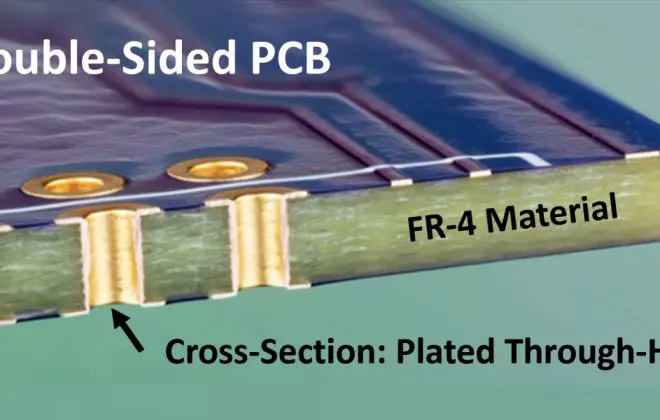

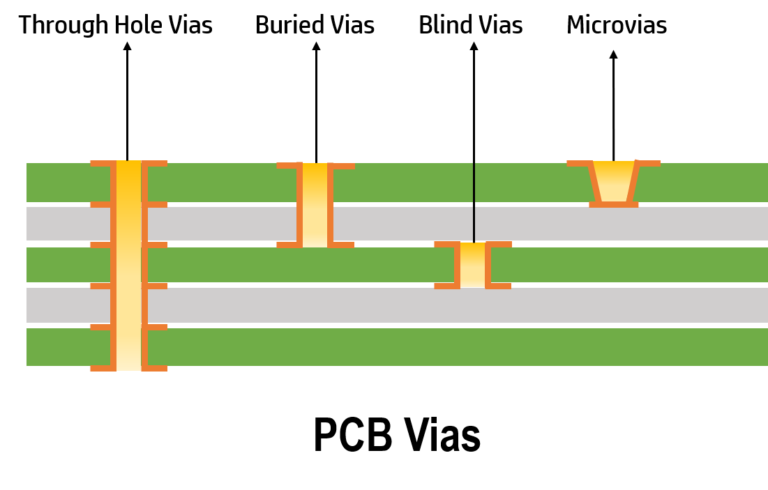

Microvias are small blind or buried vias used in high-density interconnect structures to connect adjacent layers efficiently. As defined in IPC-T-50M, they feature controlled dimensions and aspect ratios to ensure reliable fabrication. Unlike standard through-hole vias, microvias minimize board real estate usage, allowing finer pitch components and denser routing. In PCB layout, microvia placement influences electrical paths, power distribution, and mechanical stability. Poor placement can lead to signal degradation or reliability failures under thermal cycling.

The relevance of microvia placement stems from the push for miniaturization in electronics. High-speed signals require short interconnect paths to preserve signal integrity, making strategic via positioning essential. Microvias reduce stub lengths compared to through vias, lowering inductance and reflections. In multilayer stacks, they support complex topologies like BGA fanouts and fine-line traces. Optimizing microvia placement enhances PCB performance by improving impedance control and reducing electromagnetic interference. For electric engineers, this translates to fewer redesign iterations and faster time-to-market.

Technical Principles Governing Microvia Placement

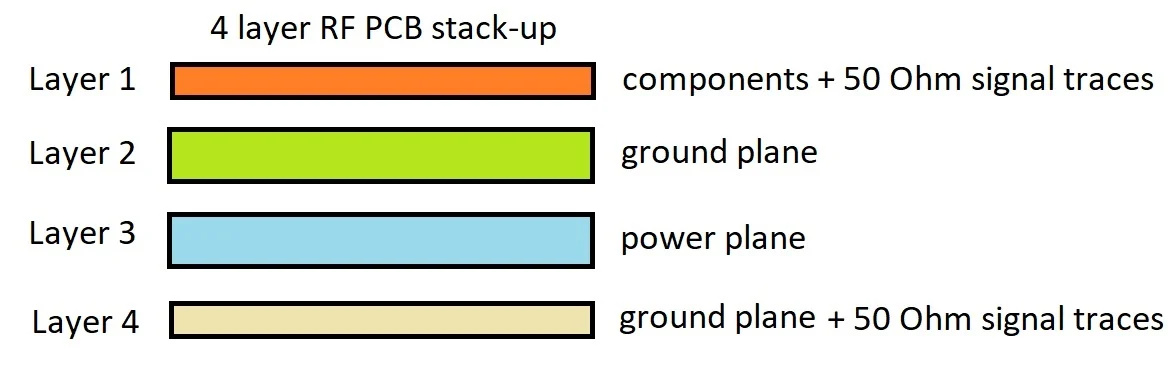

Microvia placement follows principles rooted in electrical, thermal, and mechanical behavior. Electrically, vias act as discontinuities in transmission lines, so positioning them near component pads shortens traces and maintains characteristic impedance. Signal integrity improves when microvias align with signal paths, minimizing parasitic capacitance and inductance. In high-frequency designs, via placement must account for return paths and ground planes to suppress crosstalk.

Thermally, microvias facilitate heat dissipation in dense areas, but clustered placement can create hotspots. Engineers evaluate stackup symmetry to prevent warpage, ensuring uniform via distribution across the board. Mechanical reliability depends on aspect ratios and plating thickness, as outlined in IPC-2226 for HDI designs. Stacked microvias demand precise alignment to avoid cracks during reflow. These principles guide via optimization, balancing density with long-term durability.

Fabrication constraints shape placement rules, including drill-to-drill spacing and annular ring sizes. Laser-drilled microvias require compatible dielectrics for clean sidewalls and void-free fills. In PCB layout software, rules check for overlaps and clearances prevent shorts. Understanding these mechanisms allows engineers to predict performance before prototyping.

Best Practices for Microvia Placement in PCB Layout

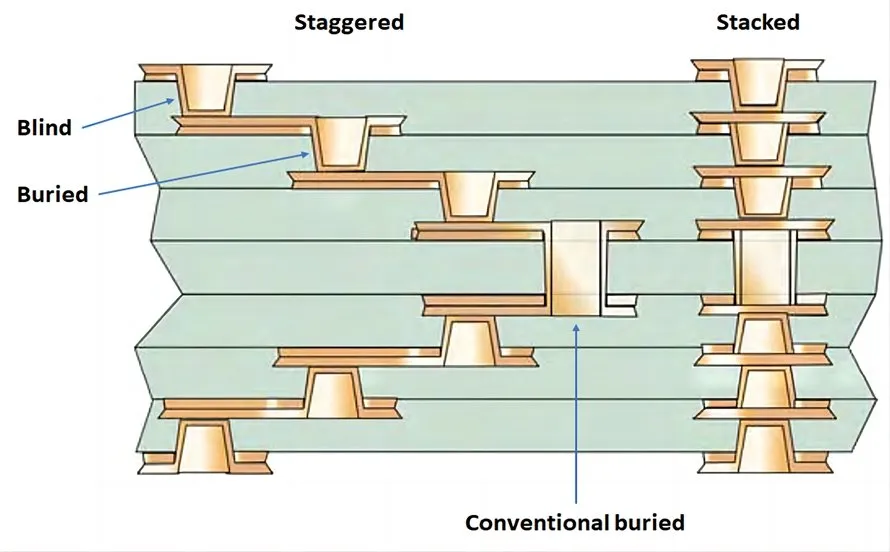

Start with stackup planning to define microvia types: blind for surface connections, buried for inner layers, staggered for multi-layer transitions, or stacked for direct vertical paths. Staggered configurations offset vias between layers to ease registration, while stacked ones suit ultra-dense needs but require robust processes. Place microvias as close as possible to the pads they serve, reducing trace lengths and impedance mismatches. This via optimization technique preserves signal integrity in high-speed interfaces.

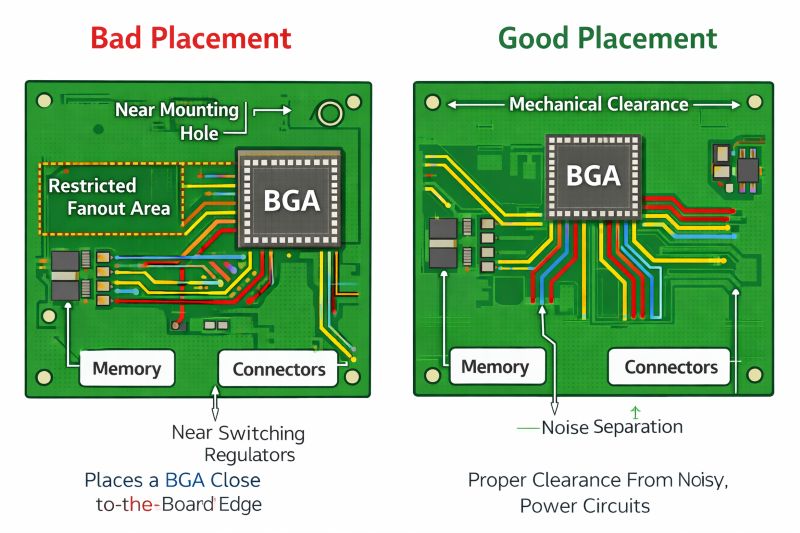

Distribute microvias evenly to avoid localized stress concentrations that could lead to delamination. Use via-in-pad designs for BGAs, filling vias with conductive epoxy or plated caps to support solder joints. Maintain adequate spacing from traces and other vias per design rules, preventing plating voids. In power delivery networks, cluster microvias under planes for low inductance paths. These practices enhance PCB performance across operating conditions.

Incorporate symmetry in microvia placement for outer layers to minimize warpage during lamination. Fanout strategies for fine-pitch components prioritize microvias over dogbones, optimizing routing density. Simulate fields early to verify signal integrity, adjusting placements iteratively. Compliance with IPC-6016 qualification specs ensures vias withstand environmental stresses like thermal shock.

Advanced Tips and Tricks for Via Optimization and Signal Integrity

For signal integrity, pair microvias with reference planes adjacent to signal layers, providing low-impedance returns. Position ground vias near signal microvias to shield against crosstalk, especially in differential pairs. Backdrill stubs if through vias interact with microvias, though HDI minimizes this need. Length-matching tools help align paths through multiple microvia transitions.

Optimize via farms for decoupling capacitors by placing arrays symmetrically around ICs, reducing loop inductance. Stagger microvias in inner layers to distribute drill loads evenly, improving yield. For mixed-signal boards, isolate analog microvias from digital ones with guard traces. These tricks elevate PCB performance in demanding applications.

Troubleshoot common issues like via opens by reviewing drill alignment and plating uniformity. If simulations show reflections, refine microvia placement to shorten paths. Thermal imaging post-assembly reveals hotspots from poor distribution. Logical iteration refines layouts systematically.

Case Study: Enhancing Signal Integrity in a High-Speed HDI Board

Consider a multilayer HDI board for data processing with 0.4mm pitch BGAs. Initial layout used through vias for fanouts, causing signal stubs and eye closure at multi-Gbps speeds. Switching to blind microvias directly under pads shortened paths, improving insertion loss. Staggered stacking connected inner layers without excessive height buildup.

Engineers adjusted placements to align with impedance targets, adding ground microvias for shielding. Post-fabrication tests confirmed cleaner eyes and lower jitter. This via optimization boosted PCB performance by 20% in margin, avoiding respins. Key lesson: simulate microvia effects early in PCB layout.

Conclusion

Mastering microvia placement transforms PCB layout from art to science, directly elevating PCB performance. Strategic positioning ensures signal integrity, reliability, and density in HDI designs. Adhere to principles like short paths, even distribution, and stackup compatibility for optimal results. Via optimization tips, from via-in-pad to shielding, provide actionable paths forward. Electric engineers benefit from these structured approaches, achieving robust boards compliant with industry benchmarks. Implement these insights to streamline your next design cycle.

FAQs

Q1: What role does microvia placement play in PCB layout for signal integrity?

A1: Microvia placement in PCB layout minimizes trace lengths and via stubs, preserving signal waveforms at high frequencies. Positioning vias near pads reduces inductance discontinuities, aiding impedance control. Ground vias nearby suppress crosstalk effectively. This via optimization maintains eye diagrams and bit error rates in HDI boards. Overall, it enhances PCB performance in demanding environments.

Q2: How can engineers optimize microvia placement for better PCB performance?

A2: Optimize by using staggered or stacked types based on density needs, ensuring even distribution to prevent stress. Place microvias in pads for compact fanouts and pair with planes for returns. Follow spacing rules to avoid fabrication defects. Simulations verify signal integrity pre-layout. These steps boost reliability and speed in PCB designs.

Q3: Why follow IPC standards in microvia placement?

A3: IPC standards like IPC-2226 provide guidelines for HDI microvia design, ensuring aspect ratios and alignments support plating and reliability. They define performance classes for qualification under IPC-6016. Adhering prevents failures like cracks or opens. This structured approach optimizes PCB layout for long-term PCB performance.

Q4: What are common pitfalls in microvia placement and how to avoid them?

A4: Clustering microvias causes thermal and mechanical issues; distribute them evenly instead. Overlooking annular rings leads to shorts, so enforce clearances. Stacked vias without fill risk voids, favoring epoxy where needed. Review stackups for warpage risks. Proactive checks in PCB layout ensure via optimization and signal integrity.

References

IPC-T-50M — Terms and Definitions for Interconnecting and Packaging Electronic Circuits. IPC

IPC-2226 — Sectional Design Standard for High Density Interconnect (HDI) Printed Boards. IPC, 2003

IPC-6016 — Qualification and Performance Specification for High Density Interconnect (HDI) Layers or Boards. IPC, 1999

ALLPCB

ALLPCB