NXP's MCX A series of microcontrollers is designed for a wide range of general-purpose applications, focusing on low cost, low power consumption, security, and reliability.

The MCXA153, the first device in this series, was released in January 2024 for entry-level MCU applications. NXP plans to expand the MCX A series to provide scalable hardware and software upgrade paths.

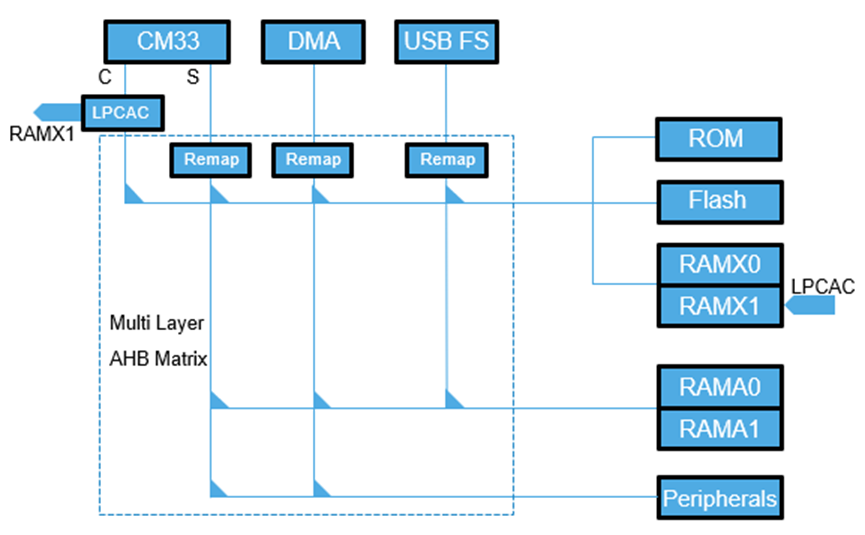

MCXA153 System Architecture

The system architecture of the MCX A series is outlined below.

The MCX A bus architecture is relatively straightforward. It features three primary bus masters: the Arm Cortex-M33 core, the DMA controller, and the full-speed USB controller. The corresponding bus targets include ROM, Flash, and RAM X, which share the code bus interface. RAM A0 and A1 share the system bus interface, and a separate bus interface provides access to peripherals.

Bus Access and Memory Map

The Cortex-M33 core primarily uses the code bus for instruction fetches and the system bus for data access. The code bus has a limited address space, allowing the M33 core to access only the ROM, Flash, RAM X0, and RAM X1. The specific address assignments can be found in the device's memory map table in the reference manual. The system bus cannot access ROM, Flash, or RAM X0/X1; it is used to access RAM A0, RAM A1, and peripherals. The DMA controller can access all peripheral spaces, while the full-speed USB controller can only access the system's memory space, not the peripherals.

Key Architectural Features

RAM Remapping

The bus architecture includes a remapping feature that allows the RAM X0 address space to be remapped to follow the RAM A1 space. This creates a contiguous RAM block of up to 32 KB to meet application requirements for larger, continuous memory areas.

4 KB Instruction Cache

The Cortex-M33 is equipped with a 4 KB cache on the code bus to accelerate Flash memory access. Due to the inherent speed limitations of Flash, a 96 MHz core clock would require two wait states for Flash access without the cache, resulting in an effective 32 MHz access speed. When the cache is enabled, a cache hit allows the M33 core to access the instruction with zero wait states, significantly improving system performance. Using the cache for instruction fetches also helps reduce overall power consumption.

ALLPCB

ALLPCB