This article addresses troubleshooting for switch-mode, low-voltage, DC-DC, single-phase, non-isolated buck converter circuits that fail to operate as expected.

General Troubleshooting Guidelines

When troubleshooting, identify active variables and reduce possible failure causes. Follow these guidelines:

- Reproduce the issue reliably to ensure it doesn't resolve and reappear unexpectedly.

- Change one variable at a time and observe the effect.

- If the circuit fails, determine what changed and check for concurrent events.

- Verify if the fault follows the converter board, chip, or load.

With these principles in mind, here are nine common issues encountered when designing DC-DC buck converters, along with potential causes.

Issue #1: Excessive Ripple

Excessive ripple may result from an inductance value that is too low. Higher inductance reduces ripple but slows transient response. Low inductance increases peak ripple current, raising the risk of inductor saturation at high temperatures and stressing the FET.

Other causes include insufficient output capacitance (Cout), which fails to support the output, or high equivalent series resistance (ESR) in Cout, causing voltage drops. Low switching frequency can also increase ripple.

Issue #2: Failure to Start

Check if the enable pin is correctly driven or pulled up and verify the power good output. Startup failure may occur due to excessive load capacitance (e.g., from an FPGA), mimicking a short circuit and triggering current limits. Some chips offer blanking or soft-start features to mitigate this.

Set the current limit as high as possible to avoid false triggers and collaborate with FPGA engineers to optimize system-level capacitance. Ensure the input voltage (Vin) remains stable and that undervoltage lockout is not activated due to input drops.

Issue #3: Voltage Present at Output When Off

If the circuit is off but voltage appears at the output, it likely originates from another power circuit. Inspect for unintended paths to other active power rails.

Issue #4: Poor Regulation

Ohmic voltage drops in the power path, often due to excessive load on a single power rail, can cause poor regulation, especially with remote voltage sensing. Using multiple converters near the load instead of a multi-rail PMIC can help.

Noisy voltage sense pins require clean layout, with related resistors placed near the controller. An unstable reference voltage due to insufficient filtering is another potential cause.

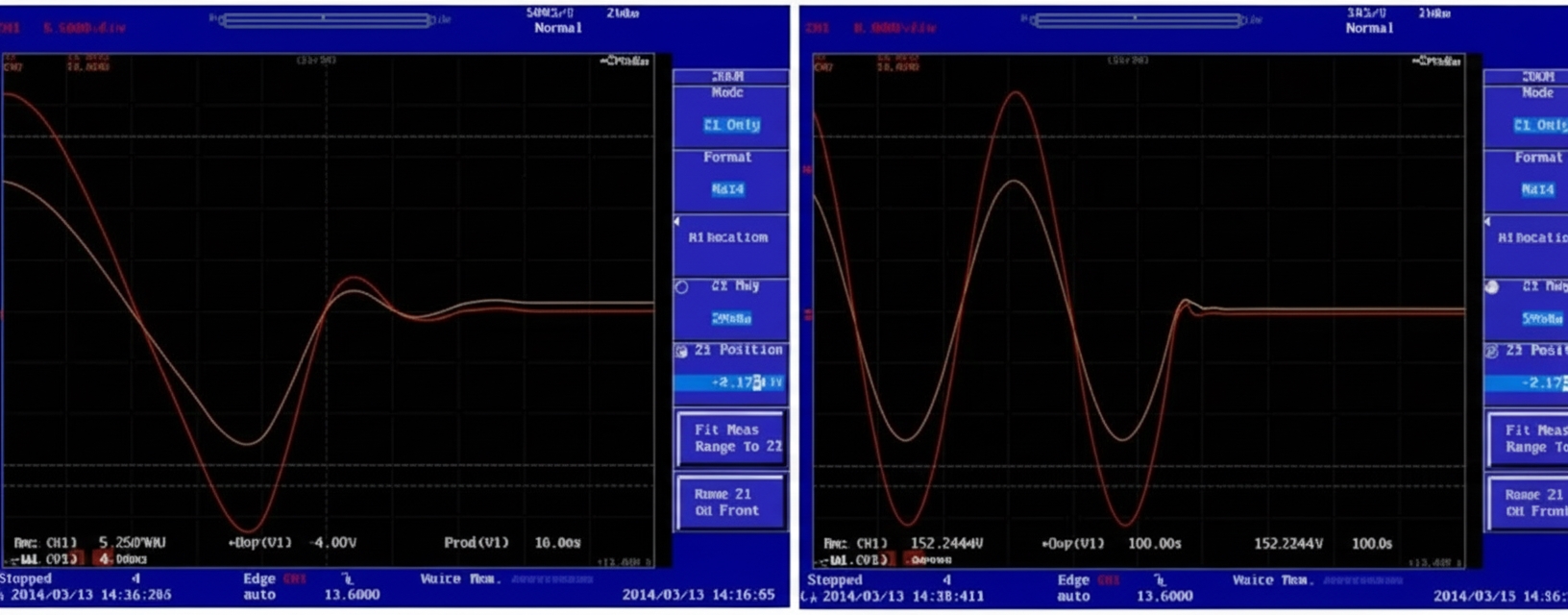

Issue #5: Slow Transient Response

Large output capacitance or inductance can slow transient response. Poor loop compensation is another factor. Without specialized equipment, characterizing loop response is challenging, but applying a step load and observing transient ringing can provide insights.

If the design load changes during development, compensation must be adjusted. For example, using a factory evaluation module at half the design load can lead to issues.

Issue #6: Instability

High Cout ESR introduces a zero in the loop response, flattening the gain curve and reducing gain margin. If the zero frequency is low enough, gain may not cross zero before the phase reaches 180¡ã. Cheaper converter chips with internal compensation require Cout ESR within a specific range for stability.

Other causes include poor voltage sensing, noisy summing node layout, or inadequate design. Use design software to generate Bode plots and verify phase and gain margins across the temperature range.

Issue #7: Low Efficiency

An undersized bootstrap capacitor may fail to fully charge the high-side FET gate, causing incomplete turn-on and power loss. A resistor in series with the bootstrap pin can control ringing.

Measuring efficiency above 90% is challenging, as it involves current measurements and power ratios. Use a spreadsheet to analyze component losses, focusing on MOSFET and inductor DC resistance (DCR), which are primary sources of heat loss.

Issue #8: Low-Temperature Issues

At low temperatures, electrolytic capacitors exhibit increased ESR and reduced capacitance, impacting performance.

Issue #9: PMBus Issues

On shared data communication buses, ensure no other node is intermittently active. Use sufficiently strong pull-up resistors (e.g., 10k¦¸ instead of 47k¦¸, as found in some FPGAs).

Conclusion

When uncertain, gather more data to support analysis, generate ideas, and facilitate team discussions.

ALLPCB

ALLPCB