Silicon carbide (SiC) MOSFETs exhibit distinct short-circuit failure characteristics compared to silicon-based IGBTs, primarily due to their shorter short-circuit withstand time and more severe degradation of electrical properties under short-circuit conditions. This article explores the reliability challenges, failure phenomena, and underlying mechanisms of SiC MOSFET short-circuit failures, providing insights for engineers and researchers in the electronics industry.

Introduction to Short-Circuit Failure Reliability

Compared to silicon-based IGBTs, SiC MOSFETs demonstrate lower short-circuit reliability, characterized by a shorter withstand time and more significant degradation of device characteristics during short-circuit events.

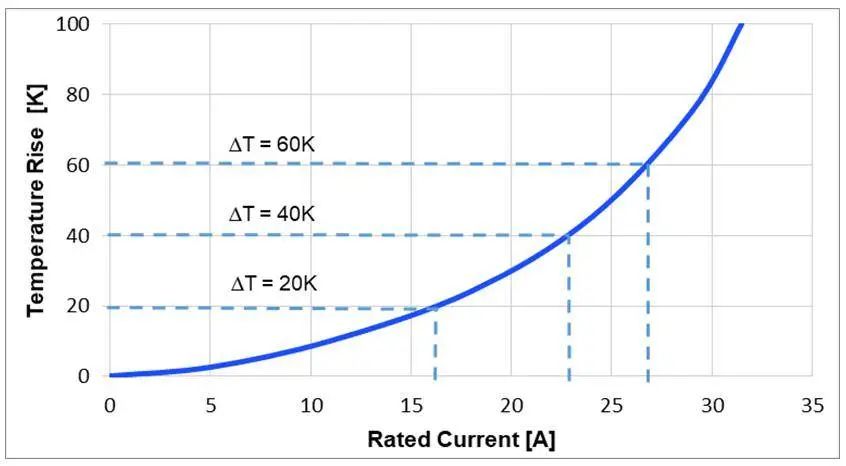

IGBT datasheets typically specify that the device can withstand a short-circuit duration of up to 10 seconds under specific stress conditions. In contrast, studies on SiC MOSFETs from manufacturers such as Cree, ROHM, and ST have shown failure occurring within 8 seconds during single short-circuit tests. This indicates that SiC MOSFETs have a shorter short-circuit withstand time, highlighting a reliability gap compared to IGBTs.

The degradation of SiC MOSFET electrical parameters under short-circuit conditions is influenced by multiple stresses, including electrical, thermal, and mechanical factors. Analyzing the degradation mechanisms requires a comprehensive evaluation of the epitaxial structure, chip packaging, and device reliability. The complexity of these mechanisms, combined with the large number of affected parameters and the extent of degradation, makes studying SiC MOSFET short-circuit reliability particularly challenging.

Two Typical Short-Circuit Failure Phenomena

Researchers have analyzed SiC MOSFET short-circuit failure phenomena through theoretical derivations, experimental observations, simulation modeling, and reverse engineering. Studies indicate that SiC MOSFET short-circuit failures typically manifest in two forms: gate-source short-circuit (G-S short-circuit) and drain-source short-circuit (D-S short-circuit). Short-circuit faults are generally classified into three types:

- Type I Short-Circuit (Hard Switching Fault, HSF): This occurs when the SiC MOSFET is already in a short-circuit loop before being turned on, entering a short-circuit state immediately upon activation.

- Type II Short-Circuit (Fault Under Load, FUL): This fault happens when a SiC MOSFET, already in the on-state, experiences a sudden short-circuit at the load, causing a short-circuit between two switching devices in different bridge arms.

- Type III Short-Circuit: In applications such as motor drives or inverters, a SiC MOSFET operating in the third quadrant may encounter a load-side short-circuit. This causes the device to rapidly transition from a low-voltage, reverse-current state to a high-voltage, high-current short-circuit state.

Failure Mechanisms

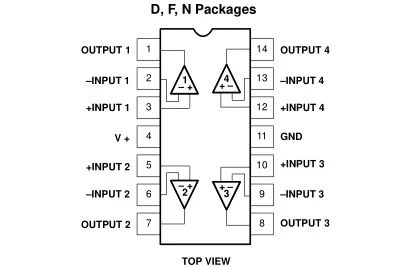

Research into SiC MOSFET failure mechanisms has progressed from surface packaging to the cellular structure of the chip. Key failure points include the JFET region gate oxide, internal parasitic NPN transistor, channel region gate oxide, and the oxide layer above the gate. Damage to the JFET region or parasitic NPN transistor typically results in a D-S short-circuit failure, while damage to the channel region gate oxide or the oxide layer above the gate leads to a G-S short-circuit failure.

One cause of SiC MOSFET short-circuit failure is high temperatures causing the source aluminum to melt. The resulting stress can damage the insulating structure of the oxide layer above the gate or the gate oxide in some cells, leading to uncontrollable short-circuit failures.

TCAD simulations have observed increased hole current in the parasitic NPN transistor region, along with current runaway phenomena consistent with experimental results. These findings confirm the possibility of parasitic NPN transistor activation. This also explains a delayed failure mode in D-S short-circuits, where the device, after being turned off, does not reduce current to zero but exhibits leakage currents of tens of amperes. The accumulated heat from the short-circuit, combined with the current from the activated parasitic NPN transistor, creates a positive feedback loop, preventing normal turn-off and leading to thermal runaway.

As a field-controlled device, a MOSFET experiences significant charge-discharge currents at the gate during switching due to the equivalent capacitance of the gate oxide. Outside of switching events, the gate typically exhibits only minimal leakage current. However, during a short-circuit, the combined effects of the gate electric field and junction temperature enhance electron tunneling and hot electron emission at the gate oxide surface, eventually reaching the critical breakdown threshold and causing gate oxide failure.

Conclusion

As SiC MOSFET applications become more widespread, research into short-circuit failure mechanisms and device reliability grows increasingly critical. Further validation is needed to confirm the accuracy and universality of various failure mechanisms and to explore their underlying causes in greater depth.

Understanding device failure and degradation mechanisms can guide improvements in device fabrication processes, short-circuit protection designs, and multidimensional reliability analysis. These advancements are essential for enhancing device lifespan and remain a key focus for ongoing research and development in the electronics industry.

ALLPCB

ALLPCB