Overview

The global memory industry is seeking new alternative technologies. Applications such as the Internet of Things, mobile devices, high-performance computing and smart vehicles have greatly increased demand for large-scale AI and edge computing, pushing existing high-capacity memories such as DRAM and NAND flash to their limits in power consumption and access speed. At the same time, advanced CMOS manufacturing has migrated to FinFET and GAA structures and node scaling beyond 14 nm, creating challenges for embedded NOR flash due to flash memory scaling limits. New embedded non-volatile memory technologies are required to match next-generation SoC, ASIC and MCU integration.

Why RRAM Is Promising

Candidate next-generation non-volatile memories include ferroelectric memory (FRAM), phase-change memory (PRAM), magnetic memory (MRAM) and resistive random access memory (RRAM). These emerging technologies typically offer read/write speeds orders of magnitude faster than NAND flash, can operate at nanoampere-scale currents, and have potential to enable in-memory computing to address the von Neumann bottleneck.

RRAM is attractive because of fast read/write, low energy consumption, simple structure, long retention, good endurance potential and low cost. Its analog conductance modulation is well suited to neuromorphic computing, making it a candidate for next-generation universal memory. Many companies and research groups are developing different RRAM variants, though most products remain in development and the underlying switching physics and optimal materials are still active research topics.

RRAM Structure and Origin

Resistive random access memory (RRAM) uses a simple metal–insulator–metal (MIM) stack. Applying voltage or current changes the resistance of the insulating layer, enabling digital storage. Early observations date back to the 1960s when changes in aluminum oxide resistance under electrical stress were reported. More recently, insulating oxides such as NiO, TiOx and HfOx have been explored as the switching layer. RRAM is non-volatile: once programmed, the resistance state is retained without an external bias until intentionally rewritten or erased.

Switching Mechanisms and Operation

The filament model is widely discussed: an initial high-voltage forming step creates a conductive path through the oxide, putting the device into a low-resistance state (LRS). The forming step typically requires a current compliance to prevent permanent damage. A reset operation interrupts the filament, returning the device to a high-resistance state (HRS). A set operation at a lower voltage than forming can reconnect the filament and restore LRS. Read operations use a small sensing voltage to discriminate LRS versus HRS.

RRAM types are often categorized as filament-type, where a continuous conductive path exists between electrodes, and interface-type, where resistance modulation is driven by changes at the electrode/insulator interface or by mobile defects across the layer. Filament-type RRAM is commonly considered the dominant conduction mechanism in many implementations.

Unipolar and Bipolar Switching

RRAM switching behavior can be unipolar or bipolar. Unipolar devices perform set and reset with voltages of the same polarity; the reset is often caused by Joule heating that ruptures the filament. Bipolar devices require opposite polarities for set and reset, typically relying on ion migration and redox reactions to modulate the filament composition.

Conduction Mechanisms in the Insulator

When high fields or temperatures are present, carriers can move through the insulating layer. Common conduction mechanisms used to interpret current–voltage behavior include:

- Ohmic conduction: free carriers in the conduction and valence bands produce a linear I–V relation at low fields.

- Schottky emission: thermal excitation of carriers over a reduced barrier at the metal/insulator interface under field-induced barrier lowering.

- Frenkel-Poole emission: field-enhanced thermal excitation of trapped carriers into the conduction band.

- Hopping conduction: carrier transport via localized defect states when many defects create overlapping energy levels.

- Tunneling: field-induced band thinning enables carriers to tunnel through the insulator.

- Space-charge-limited current: when injected carrier density exceeds recombination, charge accumulation in the insulator limits current.

Array Architectures: Crossbar, 1T1R and 1S1R

Crossbar arrays provide high density but suffer from sneak-path currents that can corrupt reads. Architectures that pair RRAM with a transistor (1T1R) or a selector device (1S1R) are used to mitigate sneak paths. 1T1R is widely used in embedded memory due to compatibility with CMOS processes and straightforward control, but scaling transistor size reduces allowable voltages, which can limit RRAM operation unless device materials and structures are optimized. Selector devices and other array-level techniques are also under development to enable high-density cross-point arrays.

RRAM for Neuromorphic and Non?Von?Neumann Computing

Neuromorphic applications attracted interest because RRAM can emulate synaptic behavior via analog conductance modulation. Key device properties for synaptic emulation include:

- Linearity: linearity of conductance update versus programming input

- Precision: achievable granularity in conductance (weight) levels

- ON/OFF ratio: dynamic range between the maximum and minimum conductance under pulsed operation

- Variation: cycle-to-cycle and device-to-device variability

- Defect rate: array yield and retention performance

Interface-type RRAM can show more linear resistance changes but may suffer retention and endurance limitations. Filamentary devices with high defect density tend to exhibit abrupt switching, behaving more like digital elements and making analog weight updates challenging. Materials engineering—for example, tuning oxygen vacancy density in HfOx or alternatives such as LiSiOx—has been explored to achieve gradual, repeatable conductance modulation.

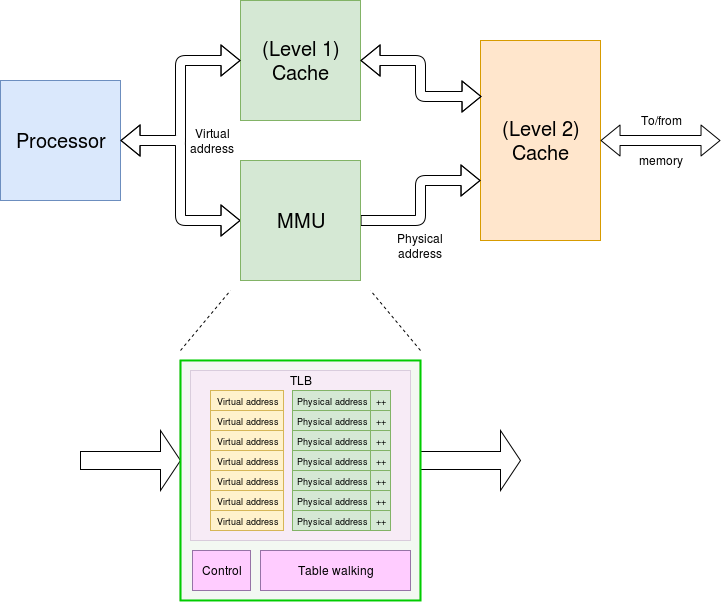

Computing-in-Memory

Traditional Von Neumann architectures separate processing and memory, creating a data transfer bottleneck. Non?Von?Neumann concepts such as computing-in-memory perform computations directly in the memory array, reducing data movement and lowering energy consumption. RRAM crossbar arrays can perform matrix-vector multiplications in analog by exploiting Ohm’s law and Kirchhoff’s current law, making them attractive for accelerating neural network inference and other linear algebra workloads.

Outlook and Challenges

RRAM offers low operating voltage, low power, and operation speeds much faster than NAND flash, with potential for high density and BEOL compatibility with CMOS processes. These characteristics make RRAM a candidate for both working memory and high-density storage, as well as for neuromorphic accelerators that integrate computation and storage.

Challenges remain in device variability, retention, endurance, selector integration to suppress sneak paths, and economic competitiveness versus entrenched technologies such as NAND flash. Cost, manufacturability, and reliability will determine which technologies achieve commercial scale. Continued research into materials, device structures, array architectures and circuit/system co-design is necessary to realize RRAM’s potential in universal memory and AI hardware.

Summary

RRAM is a leading candidate among next-generation non-volatile memories due to its simple structure, material compatibility with semiconductor processes, low power, high speed and potential for analog conductance modulation useful in neuromorphic systems. While many technical challenges remain, RRAM research spans device physics, materials, selectors, array architectures and system integration. Progress in these areas will determine the role RRAM plays in future memory hierarchies and AI accelerators.

ALLPCB

ALLPCB