Question

Why does DDR5 introduce the concept of subchannels? What is the design intent? Since a subchannel has a 32-bit data width, wouldn't forming a 64-bit cache line still require two channels to operate simultaneously?

Key concepts

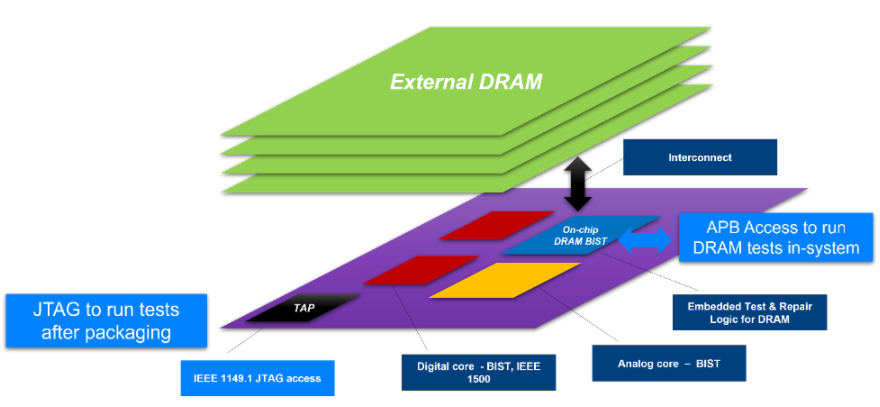

- Burst length: A burst is a sequence of consecutive data transfers within the same memory row. The number of consecutive transfer cycles is the burst length (BL). For DDR3 and DDR4, BL = 8; for DDR5, BL = 16.

- Cache line: The CPU does not read individual bytes from DRAM directly; it loads data into cache first. The cache is divided into fixed-size blocks called cache lines. The cache line is the minimum unit of transfer between memory and cache. For common x86 CPUs the cache line size is 64 bytes.

Why two subchannels in DDR5 DIMMs

With DDR4 a single channel typically has a 64-bit data path and a maximum BL of 8, so one read/write operation transfers 64 bits × 8 = 512 bits = 64 bytes, which matches the 64-byte cache line used by x86 processors.

DDR5 increases the maximum burst length to 16. If the channel data width remained 64 bits, a single burst would transfer 64 bits × 16 = 1024 bits = 128 bytes, which is larger than the traditional CPU cache line size. That larger transfer granularity would require changes across memory controller architecture and the software stack to handle the doubled transfer size.

To avoid increasing the transfer granularity, DDR5 introduces subchannels. Each subchannel has an effective data width of 32 bits; a burst of BL = 16 on a 32-bit subchannel yields 32 bits × 16 = 512 bits = 64 bytes, matching the typical 64-byte cache line. This preserves the existing transfer granularity while using the higher BL of DDR5.

ALLPCB

ALLPCB