Market Pressures and Design Challenges

Facing intense market competition, embedded systems designers must reassess development workflows. Systems are becoming more complex while constraints on performance, power, and space are tightening. Evolving standards, emerging markets, and shifting trends require a highly flexible design process that can adapt quickly. Designers need to deliver more complex systems and rapidly realize new or derivative products.

Although these demands might suggest adding development time and resources, market windows have narrowed and teams are expected to deliver more advanced, flexible systems in less time. Economic constraints often force teams to shrink rather than expand. Success requires more efficient methods to deliver feature-rich, high-performance, and adaptable products quickly.

ARM Platform Consolidation

One favorable trend for designers is the consolidation of embedded platforms around ARM processors. A few years ago the processor market was fragmented among PowerPC, RISC, MIPS, and SPARC. The market has since matured, and ARM processors have become a de facto standard in many embedded applications. As a result, a growing range of ARM-based solutions is available, from standard products to soft-core ARM IP and hardened ARM IP implemented in programmable logic and ASICs.

Even so, general-purpose embedded systems still struggle to meet modern design requirements. Multi-chip solutions are relatively straightforward to implement but are costly and lack the flexibility and power/performance metrics designers need. Single-chip solutions using soft-core processors on FPGAs are easier to implement but have limited performance. ASIC SoCs with on-chip enhanced ARM cores deliver excellent power and performance but often have long development times, low flexibility, and high costs, which delay time to market for many applications.

FPGA-Based Single-Chip Approach

To remain competitive, embedded developers need a solution that is highly flexible and efficient. FPGA-based single-chip approaches offer fast time to market and can be a compelling alternative to multi-chip and ASIC SoC solutions. Over the past decade, deployments of FPGAs with embedded processors have grown steadily. However, not all FPGA-based solutions meet stringent modern requirements. Traditionally, FPGA-based ARM systems used HDL-based soft-core processors. That approach can work for systems with modest density, power, or performance needs but may not satisfy more complex designs. For evolving systems, combining a hardened, optimized ARM core with FPGA fabric on the same platform is a stronger solution.

SoC FPGA Architecture

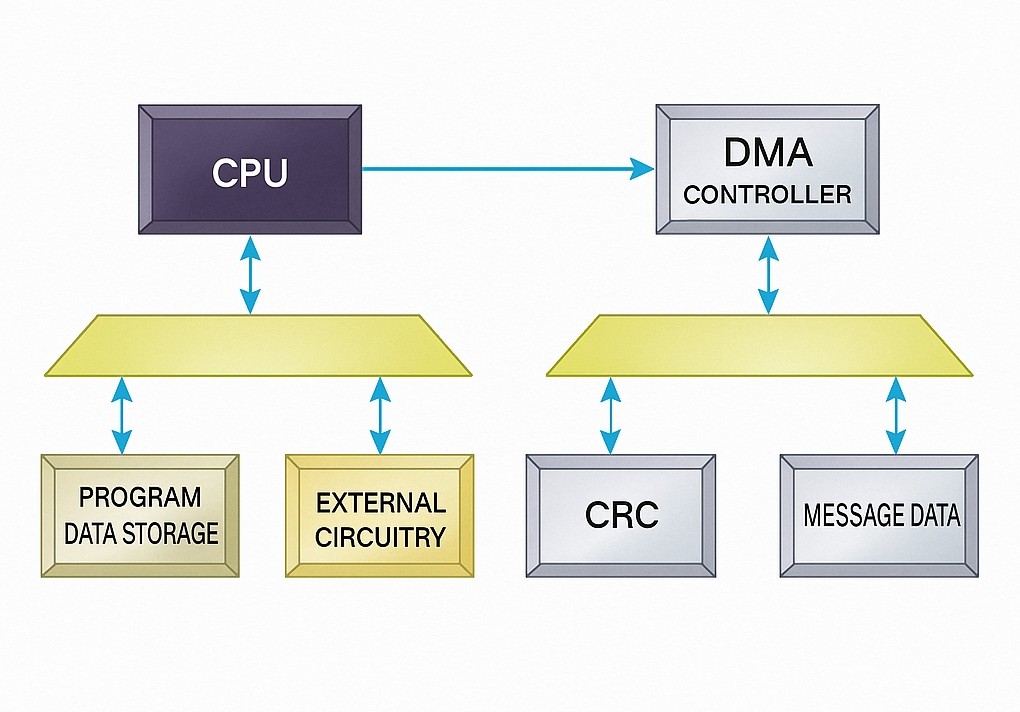

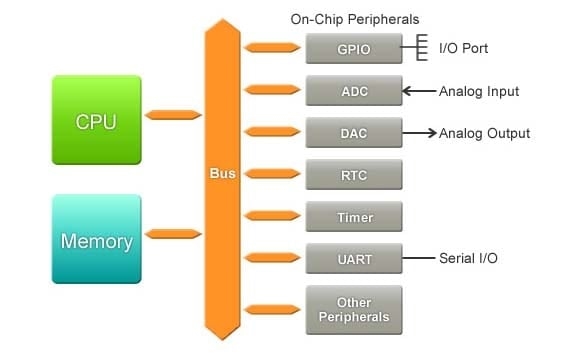

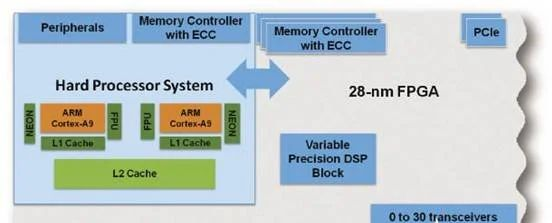

Advances by FPGA vendors have produced a class of SoC devices that address many embedded system requirements. ARM-based SoC FPGAs combine enhanced ARM processors, memory controllers, peripherals, and a customizable FPGA fabric within a single device.

An ARM-based SoC FPGA tightly integrates an optimized hardened processor system (HPS) module within the same chip as the FPGA fabric. The HPS typically includes dual-core ARM processors, multi-port memory controllers, and multiple peripheral units. Processor performance can reach about 4,000 DMIPS (Dhrystone 2.1 benchmark) with power consumption under 1.8 W. Hardened IP blocks improve performance while reducing power and cost, and they free up programmable logic resources for custom logic. The programmable fabric supports flexible communications standards and network protocols.

Figure 1

Figure 2

Figure 3

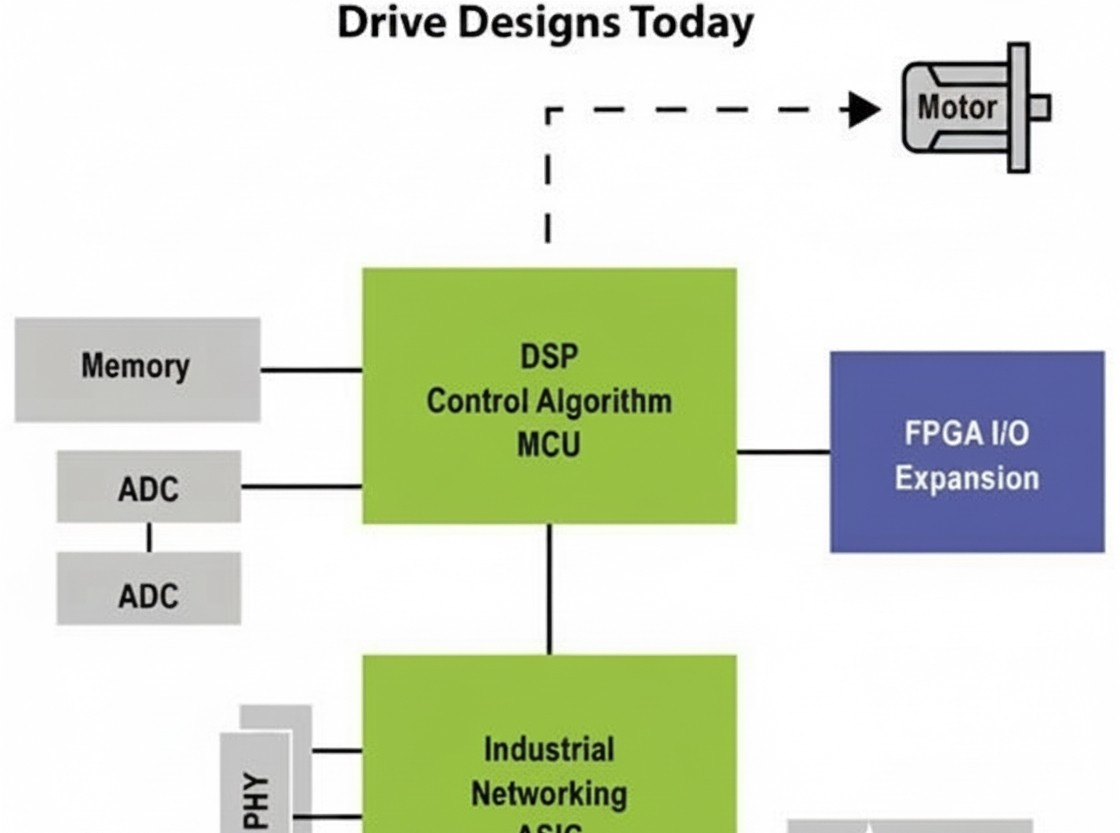

Application Example: Next-Generation Motor Drives

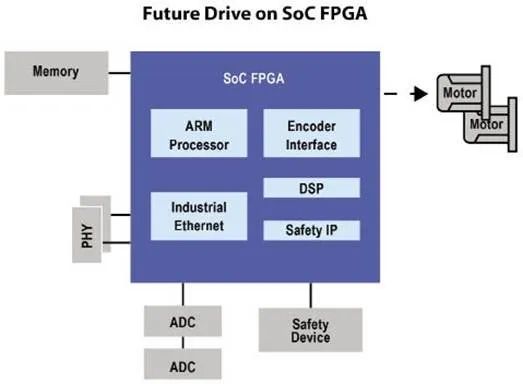

The single-chip approach can significantly improve performance and reduce power. In motor drive systems, control loop rate is a key performance metric. An SoC FPGA can achieve control loop rates 20 times faster than comparable multi-chip solutions, reducing loop time from 100 us to 5 us. This leads to notable efficiency improvements that drive most of the overall operating cost reduction. In the example described, the SoC consumes about 37% less power than a three-chip solution.

Figure 4a

Figure 4b

SoC FPGAs can reduce total system cost by integrating multiple drivers on a single chip, lowering material costs. In the cited example, a single SoC supports two motors while the multi-chip alternative supports only one. Supporting two motors on one chip reduces cost by about 53% compared with replicating the multi-chip configuration per motor. It is also straightforward to adapt the FPGA SoC to support more motors, integrate drive systems, and implement multiple protocols.

Key Points

Design teams using FPGA SoC technology can improve performance and flexibility. Hardened IP blocks deliver high performance, low power, and high density, while on-chip FPGA fabric enables rapid design iteration and customization during development or in the field. Field-programmable platforms coupled with automated and well-supported design and software tools allow teams to develop custom SoCs using commercial devices with development times far shorter than those for ASICs or multi-chip solutions. The resulting designs are flexible, updatable, and reusable, helping teams adapt quickly to new markets, changing standards, and advancing process nodes to extend product lifecycles.

Current embedded system demands have reached an inflection point where FPGA-based SoCs are a viable and advantageous option. With their combination of hardened processors and programmable logic, SoC FPGAs can help designers address difficult system challenges while achieving competitive time-to-market, cost-performance balance, and longer product lifetimes.

ALLPCB

ALLPCB