Overview

Artificial intelligence (AI) is increasingly being used to help engineers design chips. As AI gains traction in professional domains, Synopsys.ai has expanded its AI efforts and, in collaboration with Microsoft, introduced a Copilot-based generation of generative AI (GenAI) features. The collaboration integrates Azure OpenAI with Synopsys.ai GenAI capabilities, extending Copilot into electronic design automation (EDA).

Engineers are expected to leverage more advanced AI tools to improve integrated circuit design efficiency.

Copilot Background and Expansion

Copilot was originally developed by GitHub/Microsoft in partnership with OpenAI to assist software developers with coding tasks such as converting comments into runnable code, completing code blocks, and duplicating or generating methods and functions. Microsoft has significantly broadened Copilot's scope to cover areas including Microsoft 365 and solutions for sales, service, and security, as well as continued support for software developers. Given Copilot's broad impact, Synopsys chose to extend similar capabilities into the EDA domain. It is worth noting that standard Copilot already supports register-transfer level (RTL), but Synopsys aims to deliver a more powerful, domain-specific version.

Why AI Remains Emphasized

AI is considered an important tool because it offers a wide range of potential applications and can help address design challenges. Current design trends, including domain-specific architectures and multi-chip systems, are pushing product teams against the limits of Moore's Law for performance and power scaling. These approaches increase complexity in design, verification, and implementation, while teams face tighter schedules. The industry also anticipates a significant shortfall in engineering staff by 2030. AI can help address these issues through AI-enabled features in workflow tools and by providing assistance such as the Synopsys Copilot to find optimized solutions more quickly.

Synopsys.ai Copilot Capabilities

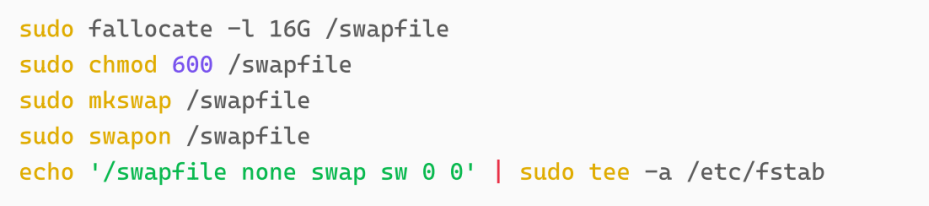

Synopsys.ai Copilot is designed to work closely with designers. Initial capabilities focus on collaboration for test engineers, offering tool knowledge, results analysis, and improved EDA workflows. Copilot also includes generative features to accelerate RTL development, creation of formal verification assertions, and development of UVM testbenches. Synopsys EDA teams plan to add more autonomous features to the Synopsys.ai suite over time, aiming for end-to-end workflows from natural language to design and manufacturing.

The assertion-generation capability for formal verification is particularly notable. Formal verification is a powerful technique but has historically been limited by the need for high-level expertise. Synopsys Copilot translates natural-language requirements written by verification engineers into correct formal syntax and suggests assertions for RTL. For RTL generation, Copilot can autocomplete code fragments and even create snippets from natural-language descriptions, which can serve as a productivity aid for less experienced developers.

Validation, Safety, and Early Access

Synopsys.ai highlights its collaboration with internal verification teams to review and vet generated code. Beyond proof-of-concept work, Synopsys.ai uses multiple techniques and years of domain knowledge to ensure generated outputs are reliable in terms of performance, power, and area (PPA) considerations.

The technology is currently in early customization, evaluation, and refinement stages and is targeted at early customers such as AMD, Intel, and Microsoft. A general release is expected after iterative improvement and validation of these capabilities to support broader use cases. Through this collaboration, Synopsys aims to accelerate product delivery while maintaining accountability for its methods and outputs.

ALLPCB

ALLPCB