Overview

It has been five years since DRAM manufacturing entered the 10 nm generation (sub-20 nm). Over the past five years, DRAM technology and product landscapes have changed significantly. This article summarizes and updates DRAM product, development, and technology trends, and addresses some misleading narratives that have circulated in technical media.

In a previous column we reviewed DRAM technology from 2000 through the early 2010s as background. This piece focuses on DRAM developments from the late 2010s to the early 2020s, corresponding roughly to the 29 nm (2X nm) to 12 nm (1β) generations. Mapping reported DRAM prototype chips presented at ISSCC to their process nodes, 29–25 nm nodes appeared around 2014, 25 nm in 2016, 21–20 nm in 2017, 22–18 nm in 2018, then continued miniaturization around 2019–2020 in the 1X/1Y nm classifications.

Key Trends

Major DRAM development trends include device scaling (smaller feature sizes), increased memory cell density, larger per-die capacities, and higher data transfer speeds (I/O). The analysis below also highlights several false or misleading claims that appear in commentary about these trends.

Is DRAM Scaling Near Its Limit?

In logic-device R&D, discussions about a "limit to scaling" are common. As noted previously, advanced logic MOSFET feature sizes no longer map cleanly to historical node names, and transistor scaling has approached practical limits. What about DRAM?

The opening chart in the original article summarized process nodes for DRAM prototype silicon presented at ISSCC from 1998 to 2023. Plotted with a linear vertical axis, the chart shows rapid scaling from 1998 to 2010 and little apparent progress since 2010, which has been interpreted as "DRAM scaling has approached its limit since the 2010s."

That interpretation contains a serious flaw: the vertical axis in that presentation is a linear measure of node size. Scaling behavior is multiplicative, not additive, so linear plots can be misleading.

Dennard Scaling and Logarithmic Trends

The proportional scaling law, often called Dennard scaling, explains the benefits of reducing MOSFET dimensions by a factor k. Dennard and colleagues showed that shrinking gate length and width by 1/k reduces delay and power roughly by 1/k, and capacitances scale accordingly, implying faster speed and lower power when devices shrink. Typical practical scaling factors correspond to k ≈ 1.4, or 1/k ≈ 0.7 per generation, meaning roughly a 30% linear reduction every technology step and a halving of linear dimensions over about six years (0.7^2 ≈ 0.49).

When the same DRAM process-node data are plotted on a logarithmic vertical axis, the picture changes: DRAM node sizes have continued to shrink at an almost constant exponential rate over 25 years, roughly halving every seven years (annual factor ≈ 0.906). This is slightly slower than the pre-1998 pace (about a six-year halving), but it shows sustained multiplicative scaling rather than a hard limit. Because node-size reduction is multiplicative, log-scale plots accurately represent long-term trends; linear plots can create the false impression of stalled progress.

Memory Density Trends

A similar misinterpretation appears when linear plots are used for memory cell density. The original article showed DRAM prototype storage density (Gbit/mm2) presented at ISSCC from 1999 to 2023 with a linear vertical axis. Viewed linearly, density seems flat from 1999 to 2010 and then rapidly increases after 2014.

That view overlooks that halving linear feature size reduces area by a factor of four, so density increases are multiplicative. When density is plotted on a log scale, the trend from 1999 to 2023 is an approximately constant exponential increase: about a 10x increase over 11 years, or an annual growth factor of roughly 1.23. This implies density roughly quadruples every 6.7 years, which aligns with the node-scaling observation of a seven-year halving of linear dimensions.

Per-Die Capacity

Maximum per-die DRAM capacity growth slowed during the 2000s. From 1995 to 2014 the maximum reported capacity at ISSCC increased about 8x over 20 years, an annual factor of roughly 1.11. Starting in the late 2010s, capacity growth accelerated again: from 2014 to 2023 the maximum capacity doubled over eight years, an annual factor of about 1.32. Examining interface families shows both DDR and LPDDR contributed to capacity increases: DDR trends reflect growing server memory demands, while LPDDR trends reflect higher capacity requirements in high-end smartphones.

Data I/O Rates

Per-pin data rates reported at ISSCC from 2000 to 2023 vary significantly by interface family. GDDR systems historically delivered the highest per-pin rates, roughly 3–4x faster than other families. HBM follows a different design philosophy: lower circuit clock rates to reduce current per pin while increasing the number of I/O pins (up to 1,024) to raise total bandwidth.

Comparing 2000–2012 and 2000–2023 trends shows differences. From 2000 to 2012, GDDR increased fastest at about 1.28x per year, followed by DDR at 1.18x and LPDDR at 1.14x. HBM was still under development by 2012 and not widely reported at ISSCC. From 2000 to 2023, HBM has shown the fastest per-pin rate growth since its first appearance in 2014, increasing at an annual factor of about 1.32 through 2022. Meanwhile, GDDR per-pin growth slowed (about 1.15x annual), and DDR also lost some momentum; LPDDR showed modest per-pin improvements.

Overall, development emphasis varies by interface family: some target higher per-pin speed while others target greater capacity and aggregate bandwidth.

Summary

This analysis compared DRAM trends from the 2000s through the early 2010s with trends in the late 2010s through the early 2020s. Key observations for the late 2010s to early 2020s are:

- Sustained multiplicative scaling of feature size and density is evident when trends are plotted on logarithmic axes; linear plots can create misleading impressions of a hard stop in scaling.

- Memory density has grown at a steady exponential rate over the long term, consistent with feature-size reductions.

- Per-die capacity growth slowed in the 2000s but accelerated again in the late 2010s, driven by both DDR for servers and LPDDR for mobile devices.

- HBM has shown rapid per-pin rate improvements since its introduction, while GDDR per-pin growth slowed as attention shifted toward aggregate bandwidth strategies.

Rising demand for higher aggregate bandwidth continues to drive HBM variants toward ultra-high-speed implementations, while GDDR per-pin speed gains have moderated.

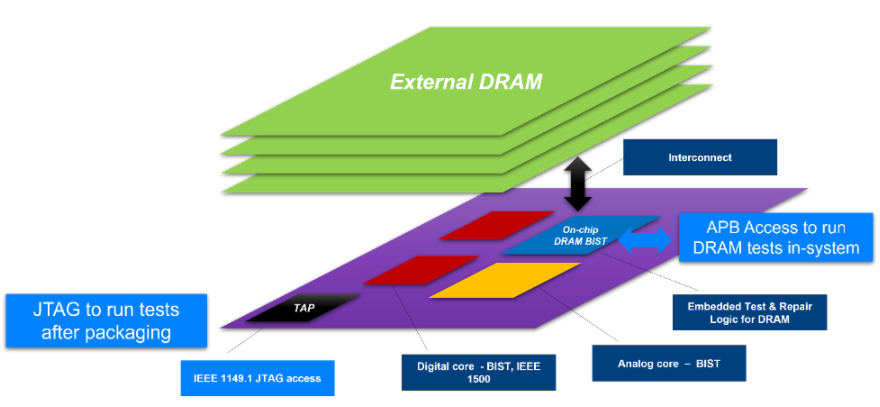

ALLPCB

ALLPCB