Overview

Overview

Yingnuoda has introduced three low-power design EDA tools within one year: the low-power design checker (LPC), the gate-level power static analysis tool (GPA), and the RTL-level power analysis tool (RPA). These releases form a multi-stage toolchain aimed at addressing power estimation and optimization across the IC design flow.

Why power reduction matters

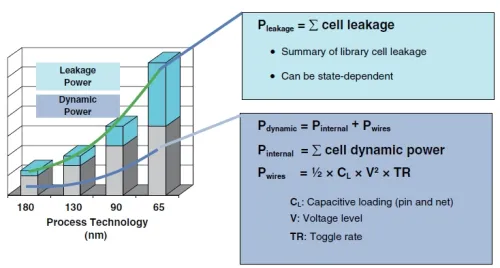

Reducing power consumption is a central topic for the semiconductor industry. Over the past decades, global electricity consumption has grown substantially, driven by changes in usage patterns and the spread of power-hungry applications such as electric vehicles, AI, 5G, machine learning, autonomous driving, and large-scale data processing. For IC designers and manufacturers, improving energy efficiency while maintaining performance is a key objective. As IC designs scale in size and complexity, rising power density becomes a limiting factor for high-performance chip development.

Industry leaders have observed that compute capability can often scale faster than improvements in energy efficiency, making power efficiency the dominant constraint in many advanced systems.

Power intent standards and design challenges

Power intent standards and design challenges

To support power-aware design, the industry uses standards such as IEEE 1801 (UPF) to describe power intent across the flow from RTL to GDS. Accurate, repeatable power data across abstraction levels (RTL, gate) and design scopes (SoC, block) is critical for teams to make informed tradeoffs and reduce iteration cost.

Early-stage (RTL) power estimation provides the greatest opportunity for effective optimization because the abstraction level allows for more flexible design changes. The earlier power considerations are integrated, the broader the set of optimization approaches that can be applied and the larger the potential savings. Conversely, late-stage optimizations are often limited in scope and effectiveness. Therefore, repeated power estimation at RTL and comparisons across architectures are necessary to improve overall energy efficiency.

Most SoC design work is performed at the register-transfer level (RTL) or by synthesizing higher-level code into standard cell libraries, some of which include low-power cells. Designers can quickly evaluate different library combinations via synthesis to meet power, performance, and area (PPA) targets. Because power affects power integrity and thermal behavior, these issues must be addressed during physical design and validated at signoff.

However, accurate early power estimation is challenging because RTL lacks detailed physical information and post-synthesis data. Designers need simulation activity data, process library files, and other reference data to converge on realistic power numbers. There is an inherent trade-off: early analysis offers higher optimization potential but lower accuracy, while late-stage analysis provides higher accuracy with reduced optimization options.

Tools to balance efficiency and accuracy

Addressing the trade-off between optimization efficiency and estimation accuracy requires comprehensive low-power design solutions with tools that balance speed and precision. Yingnuoda's EnFortius RPA static analysis tool is designed for RTL-stage power estimation, helping teams obtain accurate early power data, identify power hotspots, and refine power-management strategies to reduce circuit power.

EnFortius RPA accepts industry-standard input formats, including SystemVerilog/Verilog, Liberty cell library files, SAIF/FSDB signal activity files, and SPEF parasitic data. To improve estimation accuracy and scalability, RPA uses Yingnuoda's proprietary data and algorithm architecture, combining efficient logic synthesis, gated-clock synthesis, clock-tree synthesis engines, and a physical netmodel. This approach enables fast power computation for very large designs (equivalent to hundreds of millions of gates) and more accurate net capacitance estimation when reference physical data are available.

Supported models and analysis

EnFortius RPA implements support for:

- Common power models defined in Liberty files, including state-dependent leakage models and state- and path-dependent internal power models;

- Signal activity information from industry-standard SAIF files, including state-dependent switching activity models;

- Multi-voltage-domain power analysis for domains operating at different voltages;

- A variety of metrics and reports, such as dynamic and static power at different logical levels and groups, clock-gating ratio (CGR), and clock-gating efficiency (CGE).

Integration across the flow

Taken together, Yingnuoda's tools provide a flow for low-power management and optimization: EnFortius LPC verifies power intent across the design flow; EnFortius RPA and the gate-level power analyzer (GPA) enable early estimation and late-stage accurate measurement by consuming design netlists, activity data, and physical parameters. Signal activity data can be produced by Yingnuoda's EnCitius SVS hardware simulation accelerator to speed iterations. Yingnuoda is also developing power-optimization tools that use these analysis results to apply system-level and architectural optimizations at early stages.

ALLPCB

ALLPCB