Overview

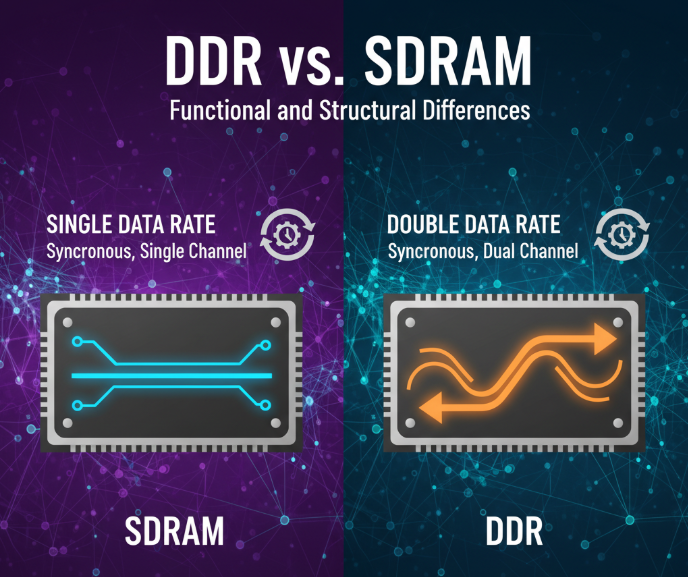

Most attention focuses on how fast DDR5 can run; this article examines why it runs reliably. Memory stability depends heavily on RAS, but not the Row Address Strobe signal. Here RAS refers to Reliability, Availability, and Serviceability. RAS features both reduce risk by adjusting signals and detect and correct errors when they occur, extending normal system operation. RAS is a set of techniques rather than a single technology; DDR5 stability benefits significantly from these features.

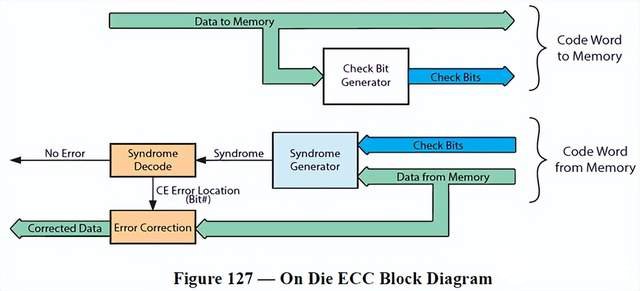

1. On-die ECC

As DDR5 signal rates increase and DRAM process complexity grows, the risk of bit errors within DRAM dies rises. DDR5 integrates on-die error correction code (ECC) into the DRAM chips to correct bit errors within the chip, improving reliability and reducing defect rates.

On-die ECC does not eliminate the need for external ECC components. It cannot correct errors that occur off-die or in the DDR channel between the module and the memory controller, so traditional side-band ECC chips may still be required in systems that need end-to-end protection.

2. Duty Cycle Adjuster (DCA)

The duty cycle adjuster allows the memory controller to compensate for duty cycle distortion between the data strobe (DQS) and data (DQ) signals by adjusting the internal duty cycle of DDR5 within a certain range. By tuning the DQ and DQS duty cycles, the DCA improves read stability.

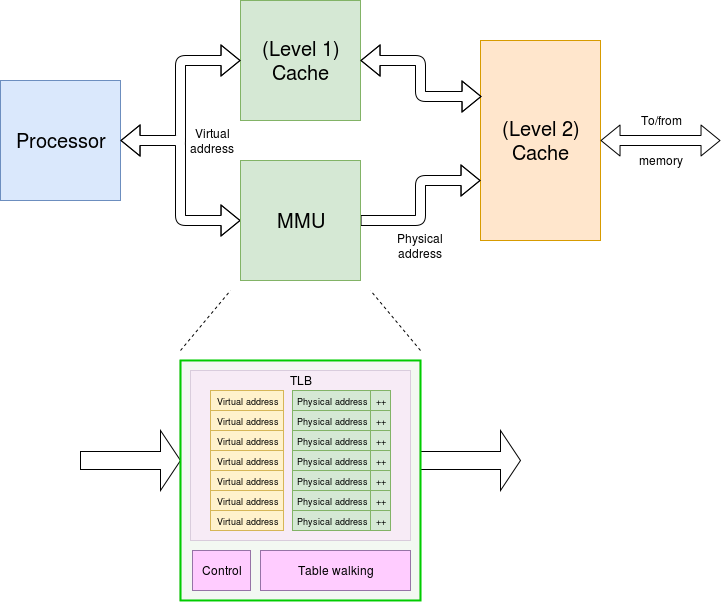

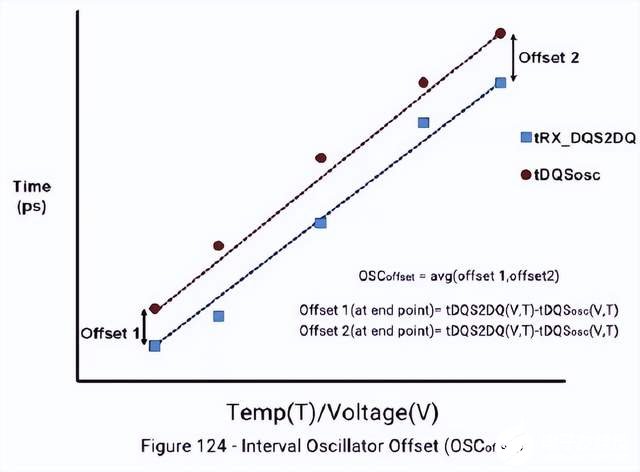

3. DQS Interval Oscillator

Voltage and temperature changes on the DDR die shift delays in the DQS clock tree and may require retraining. DDR5 includes an internal DQS interval oscillator that measures delay over a controller-specified interval. The oscillator reports whether retraining is needed and the likely error magnitude. The controller can use this information to periodically retrain channels to compensate for delay shifts caused by voltage and temperature variations.

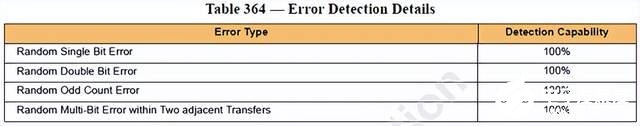

4. CRC for Read and Write

Cyclic redundancy check (CRC) is a common error-detection technique in data communications: a fixed number of check bits are appended to the data, computed by the sender and verified by the receiver. While DDR4 supported CRC only for write operations, DDR5 extends CRC to read operations as well, improving data transmission integrity.

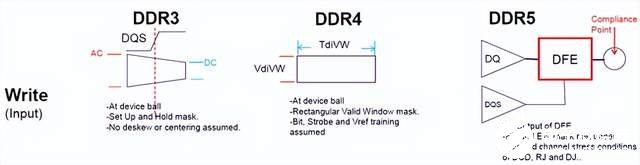

5. Decision Feedback Equalization (DFE)

To address increased data rates, DDR5 adopts decision feedback equalization (DFE), a technique previously common in high-speed serial links. DFE reduces signal attenuation and inter-symbol interference (ISI), improving eye height and supporting high-speed data transmission.

ALLPCB

ALLPCB