Switching power supplies generate noise due to rapid current transitions, impacting electromagnetic compatibility (EMC). This article analyzes noise sources in DC-DC converters, comparing external and integrated MOSFET designs, and outlines effective noise suppression strategies.

Current Paths in DC-DC Converters

Understanding noise generation requires examining current paths in a synchronous buck DC-DC converter, which uses high-side (Q1) and low-side (Q2) switches.

High-Side Switch (Q1) On

When Q1 is on and Q2 is off, current flows from the input capacitor (Cin, pre-charged) through Q1, the inductor (L), to the output capacitor (Cout) and load (Rload).

Low-Side Switch (Q2) On

When Q2 is on and Q1 is off, Cout (charged during Q1¡¯s on-state) and L maintain output current (Iout). The inductor¡¯s back-EMF initially sustains Iout, and as its energy depletes, Cout discharges through L, Rload, and Q2.

Current Path Differences

The rapid switching between Q1 and Q2 causes abrupt current changes in specific circuit loops. These transitions, combined with PCB trace inductance (approximately 1nH/mm), induce high-frequency ringing. For a 10nH inductance with a 1A current change over 10ns, the induced voltage is:

V = L * (di/dt) = 10nH * (1A / 10ns) = 1V

Parasitic Components and Noise

Parasitic elements in the circuit exacerbate noise generation, particularly in loops with rapid current changes.

Parasitic Elements

Key parasitic components include:

- Trace Inductance: Approximately 1nH/mm in PCB layouts.

- Equivalent Series Inductance (ESL): Present in capacitors.

- Parasitic Capacitance: Between MOSFET pins.

With MOSFET switching times of a few nanoseconds, these parasitics cause ringing at 100¨C300MHz, producing high-frequency switch noise. The resulting voltage and current are calculated as:

V = L * (di/dt)

I = C * (dv/dt)

Impact of Ringing

This ringing manifests as high-frequency switch noise, contributing to common mode noise at the input power supply. It can also cause crosstalk, affecting nearby circuits.

Noise Suppression Strategies

While parasitic components cannot be eliminated, noise can be mitigated through careful design. Strategies apply to both external and integrated MOSFET DC-DC converters, though external MOSFETs may introduce additional parasitics due to longer traces.

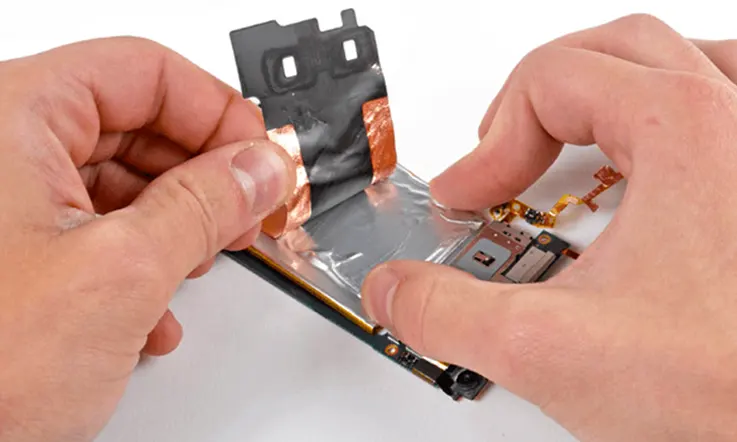

PCB Layout Optimization

Minimize loop inductance by:

- Shortening and widening PCB traces in high-current switching loops.

- Placing Cin, Q1, Q2, and L as close as possible to reduce loop area.

Integrated MOSFET designs typically have lower parasitic inductance due to compact layouts, but external MOSFETs offer flexibility for high-power applications, requiring careful trace management.

Decoupling Capacitors

Add low-ESL ceramic capacitors near the input and output to absorb high-frequency transients, reducing ringing. Integrated MOSFET designs benefit from on-chip decoupling, while external MOSFET circuits may require additional capacitors to compensate for longer traces.

Common Mode Noise Suppression

Residual noise conducts to the input power supply as common mode noise. Mitigation includes:

- Inserting high-impedance components, such as common mode choke coils, in the power line.

- Using EMI filters to block noise propagation.

External MOSFET designs may require more robust filtering due to higher parasitics, while integrated MOSFETs benefit from tighter integration but may need external filters for high-power applications.

Conclusion

Switching power supply noise, driven by rapid current changes and parasitic components, generates high-frequency ringing (100¨C300MHz). While integrated MOSFET DC-DC converters offer lower parasitics due to compact designs, external MOSFETs provide flexibility for high-power systems but require careful layout. Noise suppression relies on optimized PCB layouts, decoupling capacitors, and common mode filters. Both architectures benefit from these strategies, with external MOSFET designs needing additional attention to trace inductance and filtering to achieve comparable EMC performance.

ALLPCB

ALLPCB