Overview

Displays in wearable devices consume a large portion of battery energy. One option is to increase battery capacity, but larger batteries add size and weight and are impractical for many wearable designs as the market continues to favor smaller devices. Battery technology development has not kept pace with growing system demands, so minimizing display power consumption is a key design objective for wearable products.

Human visual perception is very sensitive, which drives manufacturers to adopt higher-resolution displays in wearables. Although several power-saving approaches exist, any reduction in visual quality directly impacts the user experience, so power-optimization strategies for displays must be chosen carefully. Higher resolution and color depth increase memory bandwidth requirements, so reducing memory power in both standby and active modes is an effective way to extend battery life.

Display System Architecture

A display consists of a pixel array where each pixel's drive value determines color. A frame buffer based on RAM stores the color information for each pixel on the display. Most common parallel displays require periodic refresh: data is read from the frame buffer and sent to the display. If display resolution and color depth are modest, the controller's internal RAM can also serve as the frame buffer.

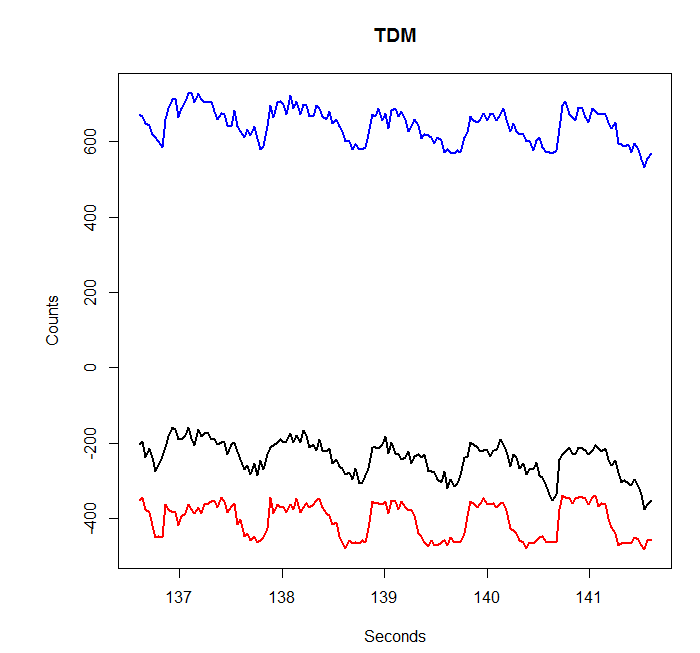

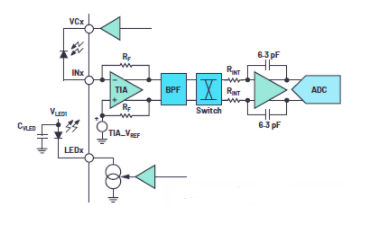

As display size, resolution, and color depth increase, internal SRAM may no longer provide sufficient capacity or performance. To avoid tearing, double buffering is often required, and frame buffers are typically implemented in external memory. During refresh cycles, data is read from the external frame buffer and output with control signals to the display controller data bus. Figure 1 shows a typical block diagram using an external frame buffer.

Figure 1: Parallel SRAM display buffer implementation (Source: Cypress)

Approaches to Reduce Display Power

Several methods can reduce display power consumption:

- Integrate the display controller into the main microcontroller. Many display modules include built-in controllers. Integration helps exploit the main microcontroller's low-power features.

- Use low-power memory for the frame buffer. Because the frame buffer is always powered, choosing memory with low standby current is important.

- Reduce frequent updates to the frame buffer. Using sufficiently large memory and loading multiple frames can lower CPU active current. Loading the most frequently accessed frames into memory avoids repeated loading and unloading from the frame buffer. Switching the frame buffer to a different memory address can change the image shown on the display.

Parallel asynchronous SRAM is commonly used as an external display buffer because controllers and displays readily support it. However, parallel memories tend to have larger package sizes and many pins. Serial memories use fewer pins and smaller packages, reducing required controller pins and lowering PCB cost. In Quad SPI mode at 108 MHz, serial memories can deliver performance comparable to parallel asynchronous SRAM. For example, Cypress Excelon F-RAM is a serial nonvolatile memory with densities up to 8 Mbit in a low-pin-count GQFN package. To optimize power it supports multiple power modes. In typical Quad SPI operation at 108 MHz, operating current is 16 mA. When the memory is idle, standby current is 102 μA. Deep standby reduces current to 0.8 μA, and sleep mode lowers it further to a minimum of 0.1 μA.

ALLPCB

ALLPCB