In the world of PCB design, a Power Distribution Network (PDN) is critical for ensuring stable power delivery to all components. One key aspect of designing an effective PDN is via placement, which directly impacts impedance and electromagnetic interference (EMI). If you're wondering how to ensure low impedance power delivery or how via placement can help avoid EMI, you're in the right place. This blog will dive deep into the essentials of PDN design, focusing on via placement strategies to achieve optimal performance.

We'll cover what a PDN is, why via placement matters, and practical tips for designing a power distribution network that minimizes impedance and reduces EMI risks. Whether you're a beginner or an experienced engineer, this guide offers actionable insights to enhance your PCB designs.

What is a Power Distribution Network (PDN)?

A Power Distribution Network, or PDN, is the system within a printed circuit board (PCB) responsible for delivering power from the source to all components. Think of it as the circulatory system of your PCB, ensuring that every chip, resistor, and capacitor gets the voltage and current it needs to function properly. A well-designed PDN minimizes voltage drops, reduces noise, and maintains signal integrity, which are all vital for high-speed and high-performance circuits.

In modern electronics, devices are becoming smaller and faster, often operating at frequencies above 1 GHz. This means the PDN must handle rapid changes in current demand without introducing noise or instability. A poorly designed PDN can lead to power integrity issues, such as voltage ripples or excessive EMI, which can degrade performance or even cause system failures.

Why Via Placement Matters in PDN Design

Vias are small holes in a PCB that connect different layers, such as power planes to components or ground planes. In the context of a PDN, vias play a crucial role in maintaining a low impedance path for power delivery. Impedance, measured in ohms, represents the opposition to current flow. High impedance in a PDN can cause voltage drops and power loss, especially in high-frequency designs where current demands spike rapidly.

Proper via placement ensures that power reaches components with minimal resistance and inductance. For example, placing vias too far from a component can increase the loop inductance, leading to higher impedance. A general rule of thumb is to keep the via-to-component distance as short as possible, ideally less than 0.5 mm for high-speed designs, to reduce parasitic effects.

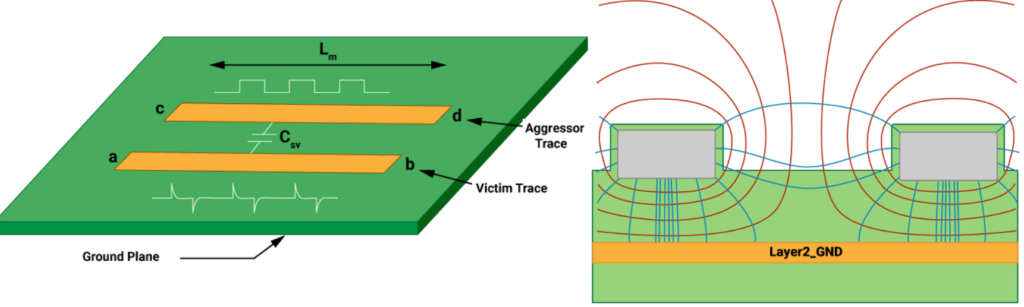

Additionally, via placement affects EMI. Poorly placed vias can create unwanted current loops, acting as antennas that radiate electromagnetic noise. This can interfere with nearby signals or even violate regulatory standards for emissions. By strategically placing vias, you can minimize these loops and improve the overall electromagnetic compatibility of your design.

How to Ensure Low Impedance Power Delivery with Via Placement

Achieving low impedance power delivery is a primary goal in PDN design. Here are some practical strategies focused on via placement to help you meet this goal:

1. Use Multiple Vias for High-Current Paths

For components that draw significant current, such as microprocessors or power ICs, a single via may not suffice. The resistance of a single via, often in the range of 1-2 milliohms, can create a bottleneck. Using multiple vias in parallel reduces the overall resistance and inductance. For instance, placing 4-6 vias around a high-current pin can cut the effective impedance by a factor of 4 or more, ensuring stable power delivery.

2. Place Vias Close to Component Pins

The closer a via is to a component's power pin, the shorter the current path, which reduces inductance. Aim to place vias within 0.3-0.5 mm of the pin for high-frequency components. This minimizes the loop area and keeps impedance low, often below 1 milliohm, which is critical for maintaining voltage stability during transient current spikes.

3. Distribute Vias Evenly Across Power Planes

In multilayer PCBs, power and ground planes are used to distribute voltage across the board. Vias connect these planes to component pins, and uneven distribution can lead to localized high-impedance areas. By spacing vias evenly, especially in high-density areas, you ensure uniform current flow. A common practice is to use a grid pattern with vias spaced every 5-10 mm across the plane, depending on the current requirements.

4. Minimize Via Length with Proper Layer Stackup

Long vias that traverse multiple layers can introduce higher inductance, typically around 1 nH per millimeter of length. To reduce this, design your layer stackup so that power and ground planes are close to the surface layers where components are mounted. This shortens the via length and keeps impedance low. For example, in a 6-layer board, placing power and ground on layers 2 and 5 can reduce via inductance compared to deeper placements.

Via Placement to Avoid EMI in PDN Design

Electromagnetic interference (EMI) is a common challenge in PCB design, especially as operating frequencies increase. Vias, if not placed thoughtfully, can contribute to EMI by creating current loops that radiate noise. Here are some via placement tips to avoid EMI:

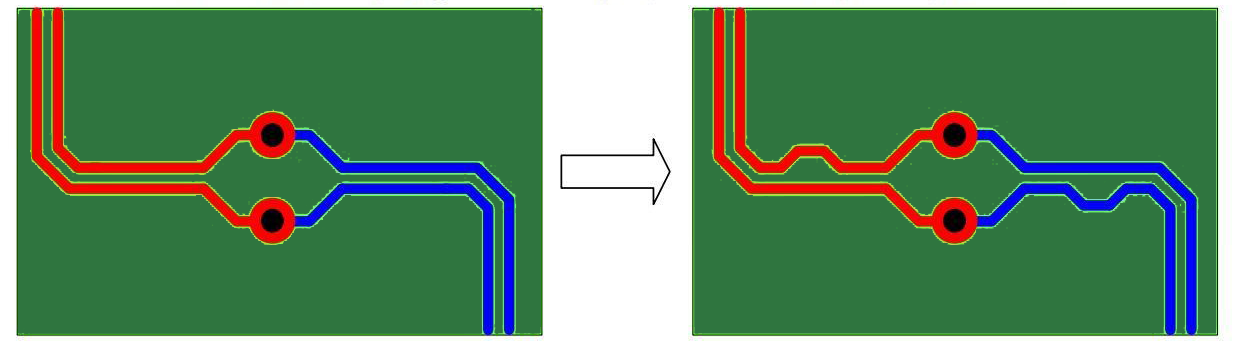

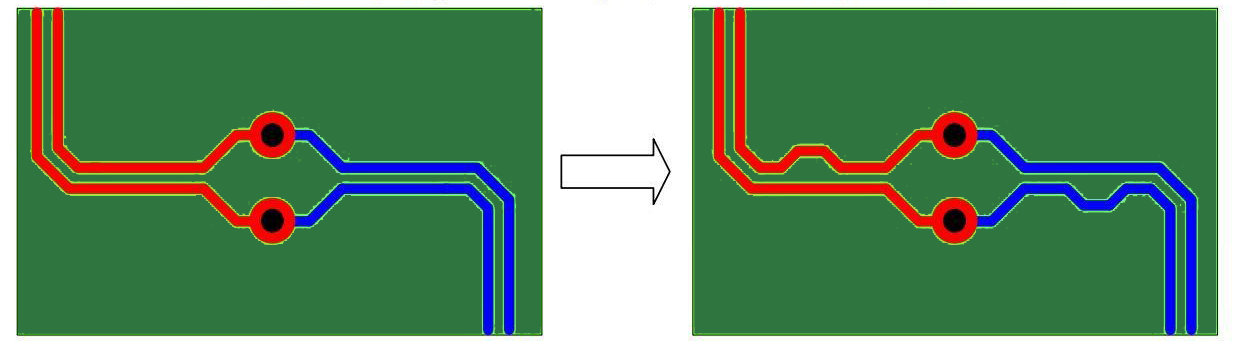

1. Pair Power and Ground Vias Closely

Placing power and ground vias close together reduces the loop area through which current flows. A smaller loop area means less radiated noise. Ideally, position power and ground vias within 1-2 mm of each other near each component. This technique can reduce EMI by up to 10 dB in high-frequency designs operating above 500 MHz.

2. Avoid Vias in Sensitive Signal Areas

If vias are placed near high-speed signal traces, they can couple noise into those signals, leading to interference. Keep vias away from sensitive areas, or use shielding techniques like ground planes to isolate them. For instance, routing signal traces on a layer separated from power vias by a solid ground plane can prevent crosstalk and EMI.

3. Use Via Stitching for Ground Planes

Via stitching involves placing multiple vias along the edges of ground planes to connect them across layers. This creates a low-impedance return path for currents and reduces the chance of ground bounce, a common source of EMI. Space stitching vias every 5-10 mm along the board edges or around critical areas to maintain a continuous ground reference, which can lower EMI levels significantly.

Designing a Power Distribution Network: Best Practices for Via Placement

Designing a power distribution network goes beyond just via placement; it requires a holistic approach to ensure power integrity. However, since vias are a fundamental part of the PDN, integrating them effectively into the overall design is essential. Below are broader best practices that tie via placement into the larger PDN design process:

1. Simulate PDN Impedance Early in Design

Before finalizing via placement, use simulation tools to analyze the impedance of your PDN across a range of frequencies, typically from DC to 1 GHz or higher. Target an impedance below 1 milliohm at critical frequencies to ensure stable power delivery. Simulations can help identify where additional vias are needed to lower impedance or suppress resonances that could amplify EMI.

2. Incorporate Decoupling Capacitors Near Vias

Decoupling capacitors help stabilize voltage by supplying quick bursts of current during transient demands. Place these capacitors close to power vias, ideally within 1 mm, to minimize inductance. Use a mix of capacitor values, such as 0.1 μF and 1 μF, to cover a wide frequency range. This combination works with vias to maintain low impedance and reduce noise.

3. Optimize Power Plane Design with Vias in Mind

Power planes should be continuous and free of splits to provide a low-impedance path. When placing vias, ensure they connect directly to these planes without creating unnecessary detours. Avoid cutting power planes with large slots or traces, as this can increase impedance and force current through longer via paths, negating the benefits of strategic placement.

Common Challenges in PDN Via Placement and How to Overcome Them

Even with careful planning, challenges can arise during PDN design. Here are some common issues related to via placement and solutions to address them:

1. Limited Board Space for Vias

In high-density designs, there may not be enough room to place multiple vias or pair them closely. In such cases, prioritize vias for high-current or high-speed components, and use smaller via sizes (e.g., 0.2 mm diameter) if manufacturing allows. Additionally, consider microvias for surface connections in dense areas to save space while maintaining low impedance.

2. Via-Induced Signal Crosstalk

Vias carrying power can couple noise into nearby signal vias or traces. To mitigate this, maintain a minimum spacing of 3-5 times the via diameter between power and signal vias. Adding a ground via between them can also act as a shield, reducing crosstalk by up to 20 dB in some scenarios.

3. Manufacturing Constraints on Via Placement

Some designs may face limitations due to manufacturing tolerances, such as minimum via spacing or drill accuracy. Work closely with your fabrication partner to understand these constraints early in the design phase. Adjust via placement rules accordingly, ensuring compliance without compromising PDN performance.

Conclusion: Mastering PDN Via Placement for Optimal Power Delivery

A well-designed Power Distribution Network is the backbone of any high-performing PCB, and via placement plays a pivotal role in ensuring low impedance power delivery and minimizing EMI. By understanding what a PDN is and applying strategic via placement techniques, such as using multiple vias, pairing power and ground connections, and integrating decoupling capacitors, you can significantly enhance power integrity in your designs.

Designing a power distribution network requires attention to detail and often simulation to validate impedance and noise levels. With the tips outlined in this guide, you’re equipped to tackle the challenges of via placement and create robust PDN systems that support the demands of modern electronics. Focus on short current paths, even via distribution, and EMI-aware layouts to achieve reliable and efficient power delivery in your next project.

ALLPCB

ALLPCB