The I2C bus is common in embedded systems. This article explains I2C bus timing.

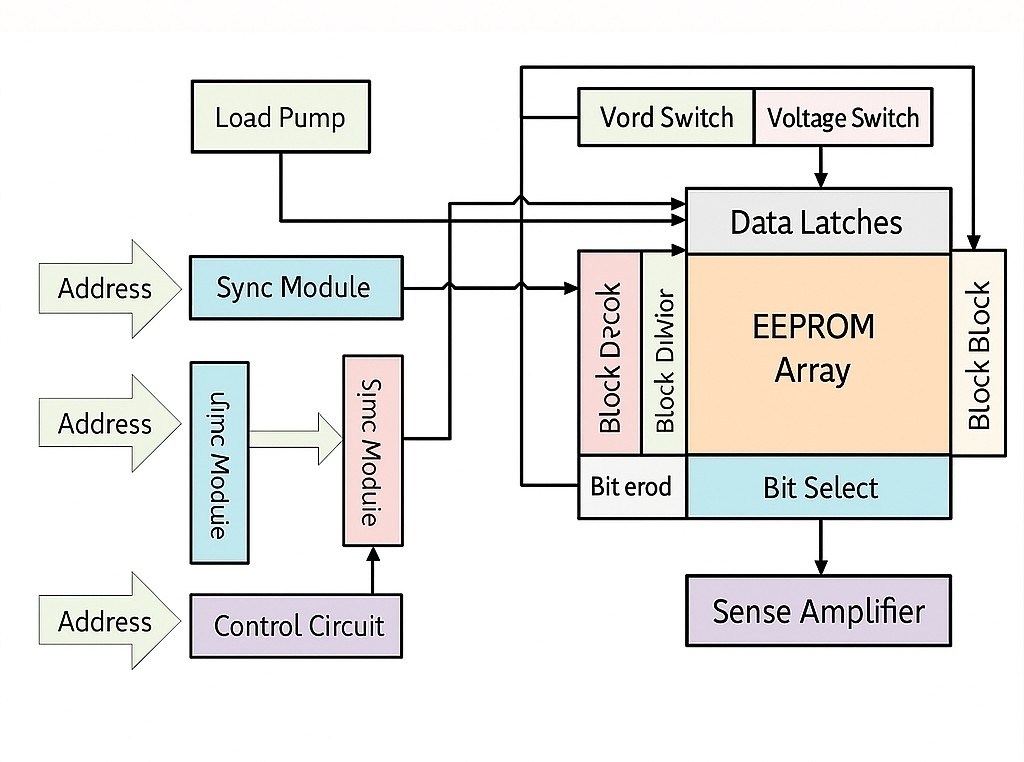

Many electronic engineers first encounter the I2C bus through EEPROM and ROM communication. In practice, I2C is used in a variety of applications beyond EEPROM memory, similar to buses such as RS-485 and SPI.

EEPROM memory system architecture diagram

1. Bit transfer

I2C is a bidirectional two-wire synchronous serial bus developed by Philips. It enables control between ICs and requires only two lines, SDA and SCL, to transfer information among devices connected to the bus.

Data on the I2C bus is transferred bit by bit. SCL is the clock line and SDA is the data line. When the SCL clock line is high, the level on SDA must not be changed. When SCL is low, the SDA data line may change state.

I2C bus bit transfer

Start condition: While SCL is high, SDA transitions from high to low. This indicates the start of a transfer.

Stop condition: While SCL is high, SDA transitions from low to high. This indicates the end of a transfer.

Idle condition: Both SDA and SCL are high. This indicates the bus is idle.

2. Data transfer

Byte transfer

When sending data, the master first sends a start signal, then configures SDA as an output and sends eight data bits, most significant bit first.

After sending the eight bits, the master switches SDA to input mode and waits for the slave device to respond with ACK or NAK before sending the next byte.

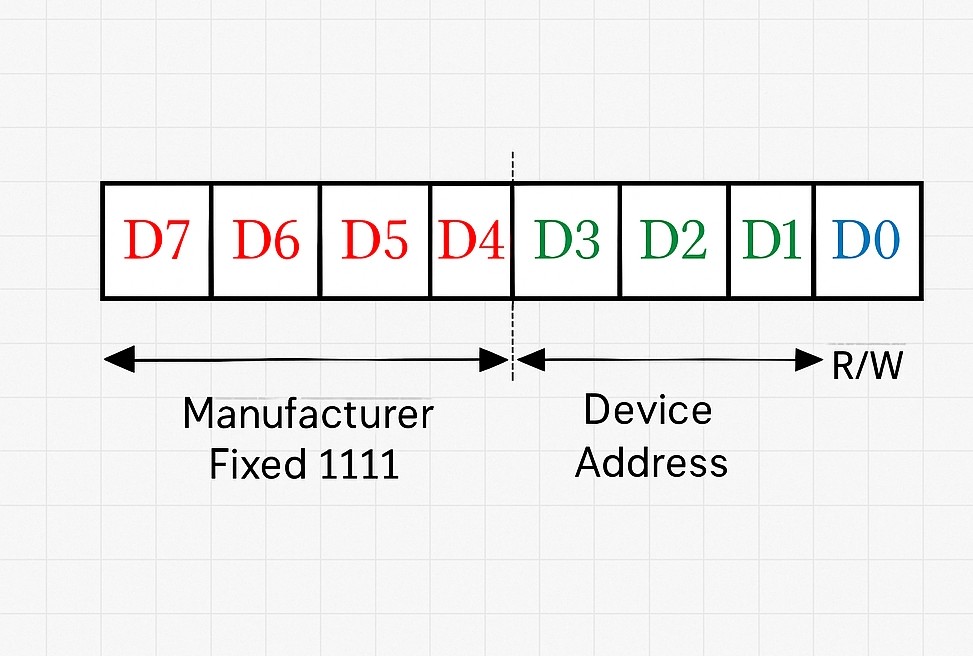

Slave device address

Each device on an I2C bus has a fixed address, usually determined by pins A0, A1, and A2 on the chip. The address byte consists of seven address bits (D7-D1) and one direction bit (D0).

D7-D4 of the device address are often fixed by the manufacturer to 1111. The remaining bits D3, D2, and D1 are set by the A2, A1, and A0 pins. D0 = 0 indicates a write operation, and D0 = 1 indicates a read operation. This explains common addresses such as 0xA0 and 0xA1.

EEPROM device address

3. Read/write procedures

1. Write sequence

- The master sends an I2C stop signal to prevent a busy bus from causing a write failure.

- The master sends an I2C bus reset signal to ensure the bus is idle before writing.

- The master sends an I2C start signal to initiate a write operation.

- The master sends the slave address with the write bit (W/R = 0) and waits for a slave ACK.

- After receiving ACK, the master writes multiple bytes. After each byte, the master waits for a slave ACK.

- After receiving the final ACK, the master sends an I2C stop signal to ensure the bus is idle.

2. Read sequence

- The master sends an I2C stop signal to prevent a busy bus from causing a read failure.

- The master sends an I2C bus reset signal to ensure the bus is idle before reading.

- The master sends an I2C start signal to initiate a read operation.

- The master sends the slave address with the read bit (W/R = 1) and waits for a slave ACK.

- After receiving ACK, the master reads multiple bytes. After each received byte, the master sends an ACK back to the slave.

- After the final byte and ACK, the master sends an I2C stop signal to ensure the bus is idle.

I2C is widely used in embedded applications and is common in many power electronics devices.

ALLPCB

ALLPCB