In the fast-paced world of mobile phone technology, ensuring signal integrity in PCB layout is critical for reliable performance. Signal integrity issues can lead to data loss, delays, or device failure, especially in high-speed designs. But what causes these problems, and how can they be solved? In this blog post, we’ll explore common signal integrity challenges in mobile phone PCB layouts, such as PCB signal reflection, impedance mismatches, and crosstalk, along with practical solutions like impedance matching, crosstalk reduction, and signal integrity simulation.

Whether you’re an engineer working on high-speed PCB design or a designer looking to optimize mobile phone circuitry, this guide offers actionable insights to tackle these issues head-on. Let’s dive into the details of signal integrity and how to maintain it in compact, complex mobile phone layouts.

What Is Signal Integrity in Mobile Phone PCB Layout?

Signal integrity refers to the ability of a signal to travel through a printed circuit board (PCB) without distortion, interference, or loss. In mobile phones, where space is limited and components operate at high frequencies, maintaining signal integrity becomes a significant challenge. Modern devices often transmit data at speeds exceeding 5 Gbps, making even minor layout flaws capable of disrupting performance.

Signal integrity issues can manifest as delayed signals, incorrect data transmission, or electromagnetic interference (EMI). These problems not only affect user experience but can also lead to costly redesigns. Understanding the causes of signal integrity issues in mobile phone PCB layouts is the first step toward creating robust designs that meet today’s high-speed demands.

Common Causes of Signal Integrity Issues in Mobile Phone PCBs

Mobile phone PCBs are packed with high-speed components like processors, memory chips, and wireless modules. The compact nature of these designs amplifies the risk of signal integrity issues. Below are the primary causes, focusing on key challenges like PCB signal reflection and impedance mismatches.

1. PCB Signal Reflection Due to Impedance Mismatches

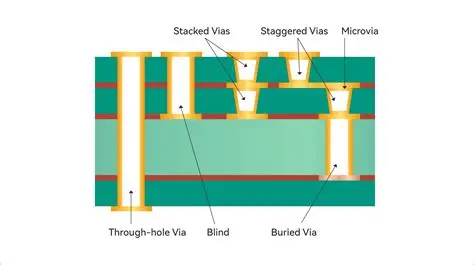

Signal reflection occurs when a signal encounters a sudden change in impedance along its path, causing part of the signal to bounce back. In mobile phone PCBs, this often happens at connectors, vias, or improperly terminated traces. Reflections can distort the signal, leading to errors in data transmission. For instance, at frequencies above 1 GHz, a mismatch of just 10 ohms can cause significant reflection losses.

The root cause of PCB signal reflection is often poor impedance matching between components, traces, and terminations. Without consistent impedance, signals cannot travel smoothly, resulting in degraded performance.

2. Crosstalk Between Adjacent Traces

Crosstalk is the unwanted coupling of signals between nearby traces, a common issue in densely packed mobile phone PCBs. When traces run parallel for long distances, electromagnetic fields from one trace can interfere with another, introducing noise. This is particularly problematic in high-speed PCB design, where data rates are high, and even small interference can corrupt signals.

For example, in a mobile phone PCB, a trace carrying a 2.4 GHz Wi-Fi signal might induce noise in a nearby trace handling audio data, leading to poor call quality. The closer the traces and the higher the frequency, the greater the risk of crosstalk.

3. Improper Grounding and Return Paths

A solid grounding strategy is essential for signal integrity, but mobile phone PCBs often suffer from split ground planes or poorly designed return paths. When a signal’s return path is interrupted—say, by a gap in the ground plane—it can create loops that act as antennas, radiating EMI and degrading signal quality.

In high-speed designs, signals above 500 MHz are especially sensitive to return path issues. Without a continuous ground plane, signals may take unintended paths, increasing noise and delays.

4. High-Speed Design Challenges

High-speed PCB design in mobile phones involves signals operating at gigabit-per-second speeds, such as USB 3.0 or 5G interfaces. At these frequencies, even tiny layout errors—like a trace length mismatch of 1 mm—can cause timing issues or signal skew. The compact size of mobile phone PCBs makes it harder to manage trace lengths and spacing, amplifying these high-speed design challenges.

Impact of Signal Integrity Issues on Mobile Phone Performance

Signal integrity issues don’t just affect individual components; they impact the entire device. For instance, PCB signal reflection can cause data errors in memory chips, leading to app crashes. Crosstalk might degrade wireless signals, resulting in dropped calls or slow internet speeds. EMI from poor grounding can interfere with nearby devices, failing regulatory standards.

Moreover, these issues can increase power consumption as the device struggles to compensate for signal errors, draining the battery faster. For manufacturers, resolving signal integrity problems after production is costly and time-consuming, often requiring complete redesigns. Addressing these challenges during the design phase is crucial for both performance and cost efficiency.

Effective Solutions for Signal Integrity in Mobile Phone PCB Layout

Now that we understand the causes, let’s explore practical solutions to maintain signal integrity in mobile phone PCB layouts. These strategies focus on impedance matching, crosstalk reduction, and leveraging tools like signal integrity simulation for high-speed PCB design.

1. Impedance Matching for Reduced Signal Reflection

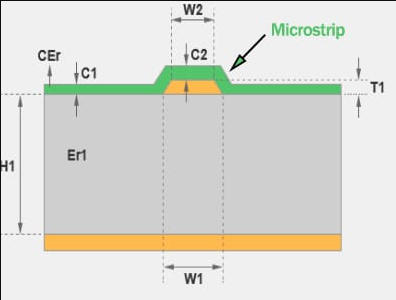

Impedance matching ensures that the impedance of traces, components, and terminations remains consistent across the signal path. To achieve this in mobile phone PCBs, designers must calculate the characteristic impedance—typically 50 ohms for high-speed signals—and design traces accordingly.

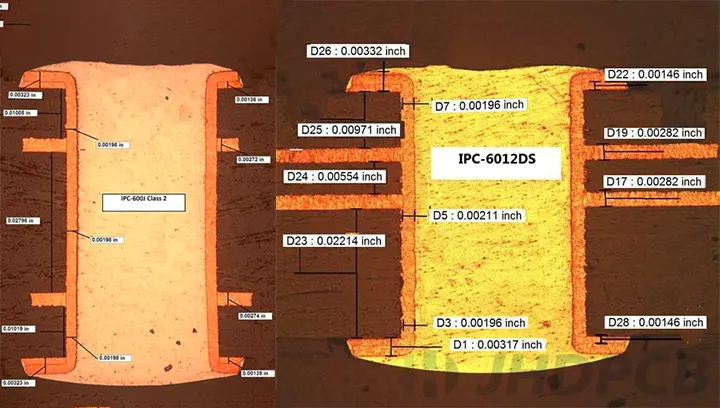

Use controlled impedance traces by adjusting their width and spacing based on the PCB stack-up and dielectric material. For example, a trace width of 5 mils on a standard FR-4 material with a 4-layer stack-up can maintain 50-ohm impedance. Additionally, place termination resistors close to the receiving end of high-speed signals to absorb reflections.

Tools for signal integrity simulation can help predict and adjust impedance before manufacturing, saving time and reducing errors. By prioritizing impedance matching, you can significantly minimize PCB signal reflection and ensure smooth signal transmission.

2. Crosstalk Reduction Through Layout Optimization

Crosstalk reduction starts with careful trace routing. Keep high-speed traces as short as possible and avoid running them parallel for long distances. If parallel routing is unavoidable, increase the spacing between traces—aim for at least 3 times the trace width to minimize electromagnetic coupling.

Another effective method is to use guard traces, which are grounded traces placed between sensitive signals to act as a shield. Additionally, ensure a solid ground plane beneath signal layers to provide a low-impedance return path and reduce interference. For instance, in a mobile phone PCB, spacing critical traces by 15 mils instead of 5 mils can reduce crosstalk by up to 30% at 1 GHz frequencies.

3. Solid Grounding and Return Path Design

A continuous ground plane is vital for high-speed PCB design in mobile phones. Avoid splitting the ground plane under high-speed signals, as this disrupts the return path and increases EMI. If splits are necessary for power distribution, use stitching capacitors or vias to bridge the gap and maintain a low-impedance path.

Place ground vias strategically near high-speed components to shorten return paths. For example, placing vias within 10 mils of a high-speed IC’s ground pin can reduce loop inductance by 50%, minimizing noise. A well-designed grounding strategy stabilizes signals and enhances overall device reliability.

4. Signal Integrity Simulation for High-Speed PCB Design

Signal integrity simulation is a powerful tool for identifying and resolving issues before manufacturing. These simulations analyze factors like signal reflection, crosstalk, and timing delays, allowing designers to optimize layouts early in the process. For mobile phone PCBs, where high-speed signals are common, simulation can predict how a 3 Gbps signal will behave across a specific trace length and adjust for potential issues.

Simulation tools can model impedance mismatches, test different trace routings, and evaluate the impact of vias or connectors. By running simulations, designers can save weeks of debugging time and ensure the PCB meets performance standards. Incorporating signal integrity simulation into the design workflow is essential for tackling the complexities of high-speed PCB design.

5. Decoupling Capacitors for Power Integrity

Power integrity directly affects signal integrity. Voltage fluctuations or noise on power lines can distort high-speed signals in mobile phone PCBs. Decoupling capacitors, placed close to power pins of ICs, help filter out noise and stabilize voltage levels. For instance, a 0.1 μF capacitor near a processor’s power pin can reduce voltage ripple by up to 90% at frequencies below 100 MHz.

Use multiple capacitors of different values (e.g., 0.01 μF, 0.1 μF, and 1 μF) to cover a wide frequency range. Position them within 50 mils of the target pin for maximum effectiveness. This approach ensures clean power delivery, supporting signal integrity across the board.

Best Practices for High-Speed PCB Design in Mobile Phones

Beyond specific solutions, adopting best practices during the design phase can prevent signal integrity issues from arising. Here are key tips tailored for mobile phone PCB layouts:

- Minimize Via Usage: Vias introduce impedance discontinuities. Use them sparingly and opt for back-drilled vias in high-speed designs to reduce stub effects.

- Optimize Stack-Up Design: Use a multi-layer stack-up with dedicated ground and power planes. A 6-layer PCB with signal-ground-power-signal-ground-signal configuration can improve shielding and reduce noise.

- Match Trace Lengths: For differential pairs like USB or HDMI signals, ensure trace lengths are matched within 5 mils to avoid timing skew.

- Avoid Sharp Corners: Route traces with 45-degree angles instead of 90-degree turns to prevent signal reflection and EMI.

- Test Early and Often: Use signal integrity simulation at multiple stages of design to catch issues before they escalate.

Why Signal Integrity Matters More Than Ever

As mobile phones evolve with 5G, AI, and IoT capabilities, the demand for high-speed PCB design continues to grow. Frequencies are increasing, with 5G signals operating at 28 GHz and beyond, while board space shrinks to accommodate more features. This combination makes signal integrity a top priority for engineers. A single oversight in impedance matching or crosstalk reduction can render a device unusable in competitive markets.

By addressing signal integrity issues early—through careful layout, simulation, and best practices—designers can create mobile phone PCBs that deliver reliable performance under the toughest conditions. The investment in time and tools pays off with fewer redesigns, lower costs, and satisfied users.

Conclusion

Signal integrity issues in mobile phone PCB layouts, such as PCB signal reflection, crosstalk, and impedance mismatches, pose significant challenges in high-speed PCB design. However, with the right strategies—impedance matching, crosstalk reduction, solid grounding, and signal integrity simulation—these problems can be effectively managed. By following best practices and leveraging advanced tools, engineers can ensure their designs meet the demands of modern mobile technology.

At ALLPCB, we’re committed to supporting your journey in creating cutting-edge mobile phone designs. Whether you’re tackling high-speed signals or optimizing compact layouts, understanding and addressing signal integrity is the key to success. Start applying these solutions today to build reliable, high-performing PCBs for the devices of tomorrow.

ALLPCB

ALLPCB