Early predictions and momentum

In March 2023, David Patterson, the principal architect of RISC-V and a Turing Award winner, predicted at the Pingtouge XuanTie RISC-V ecosystem conference that "in 3–5 years, RISC-V will be everywhere." In June 2023, Krste Asanovi?, co-founder and chief architect of SiFive and a principal inventor of RISC-V, said at a SiFive RISC-V China technology forum that "within 2–3 years, RISC-V will break performance or application limits and quickly surpass all other architectures."

By the numbers, according to the RISC-V International Foundation, as of July 2023 RISC-V had over 3,820 global member organizations, rising to nearly 4,000 by August 2023 across more than 70 countries. Shipment estimates indicate 10 billion units by the end of 2022 and an expectation of 60 billion by 2025, meaning RISC-V reached a scale in about 12 years comparable to 30 years of development for traditional ISAs.

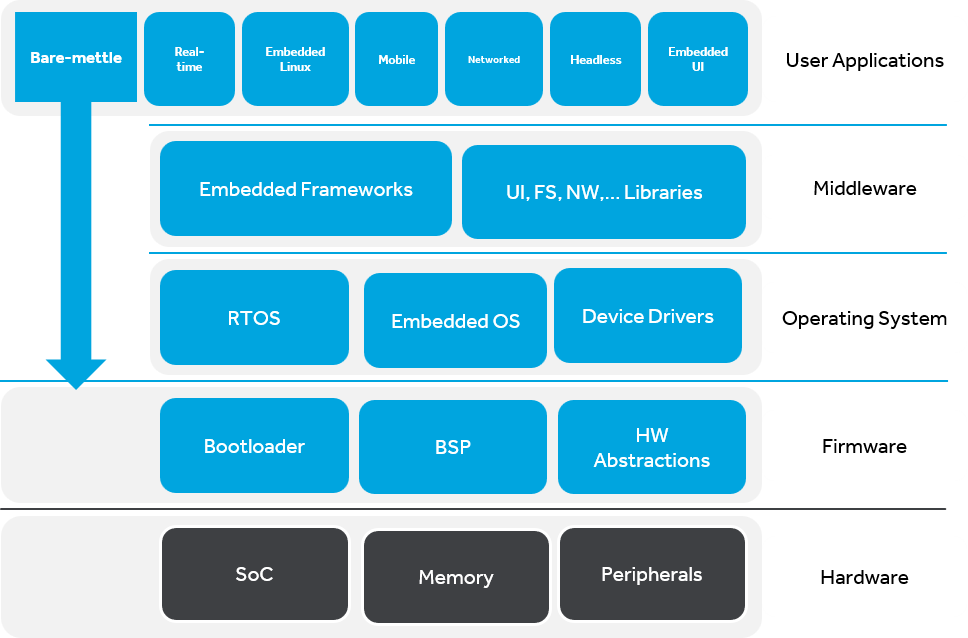

From an ecosystem perspective, RISC-V has expanded beyond IoT and microcontroller applications into higher-performance domains such as servers, mobile devices, and automotive electronics. Software and tools for specific domains like DSP, AI, imaging, and networking have also been developing steadily.

RISC-V showing up in automotive and servers

At the third Drip Lake China RISC-V Industry Forum on August 28, 2023, RISC-V server chips appeared alongside automotive RISC-V projects. This indicates that, in the Chinese market, RISC-V implementations in automotive systems emerged before server deployments, but that timing alone does not imply servers are easier or harder to adopt.

Why use RISC-V cores?

Tenstorrent Inc. lead CPU architect Lian Weihang said that after major automakers began designing in-house vehicle chips, demand for custom automotive compute surged. He argued that modern vehicles resemble smartphones on wheels and that onboard systems are becoming the new battleground for differentiation. For automakers, customized instruction sets allow deep coupling between software, hardware, and product differentiation. Since vendors such as Intel and AMD do not provide customized ISA extensions and ARM typically licenses fixed IP cores, RISC-V offers the openness and customizability needed for differentiated automotive designs.

Recent industry activity supports this trend: Qualcomm, NXP, Infineon, Nordic, and Bosch announced a joint statement to invest in a chip company focused on RISC-V architecture to support next-generation hardware development. Observers suggest Qualcomm's move toward RISC-V may be related to disagreements with ARM licensing and a desire for a more open, customizable ISA.

Server requirements and RISC-V advantages

In the server domain, x86 processors still dominate PC and server markets, while ARM dominates mobile. However, cloud computing imposes distinct demands. x86 faces heavy backward compatibility constraints that limit optimization for cloud workloads. Cloud-focused chips must add features for critical cloud tasks to improve performance and remove unneeded legacy features to reduce power consumption.

Video cloud workloads illustrate this: video encoding has high but uneven compute demand across I, P, and B frames. Traditional CPU approaches that increase clock frequency can encounter unstable compute requirements, potentially triggering throttling and reducing encoding throughput. RISC-V and ARM-based designs can offer more stable throughput and better resource allocation, reducing the need for large performance headroom reserved to avoid throttling.

Additionally, traditional CPUs often have relatively few logical cores with features such as hyperthreading, while RISC-V and ARM-based designs can scale to many more cores, in some cases tens to hundreds, similar to GPU-like scaling. This allows matching core counts to diverse workloads, yielding better utilization and lower cost for cloud operators.

One compelling server advantage of RISC-V is the ability to add custom instruction extensions to an open, royalty-free ISA. Ventana Micro Systems CEO Balaji Baktha described how custom instructions can be implemented as small hardware accelerators visible to the processor. This makes it easier and cheaper to design SoCs with custom accelerators than licensing CPU cores and integrating custom functionality under more restrictive IP terms. The custom instructions and connectors remain proprietary to the chip designer, enabling differentiation.

Automotive vs. servers: which will land first?

Historically, before 2020 RISC-V had almost no presence in servers, but the industry now sees strong server potential. An investment forecast suggested ARM and RISC-V could replace x86 as the dominant server processors by 2030, with ARM and RISC-V combinations gaining significant market share in cloud data centers.

Red Hat senior software engineer Fu Wei believes RISC-V will be easier to deploy in servers than in vehicles. He noted that automotive chip certification is complex and demanding because failures can affect human safety, while servers can rely on redundancy and backups, lowering regulatory barriers.

From a deployment scale point of view, server workloads are large and concentrated in the cloud, offering economic and energy-efficiency incentives to replace legacy architectures. RISC-V International has identified HPC as a strategic priority for RISC-V growth.

Early server attempts struggled due to immature software ecosystems and less advanced process technology. Applied Micro failed in earlier attempts, but in December 2022 Ventana Micro Systems introduced the Veyron V1, marking a significant step. In SPECint 2017 tests, Ventana reported that the 128-core Veyron V1 outperformed a 64-core AMD EPYC Milan 7763 at comparable or higher power consumption and matched or exceeded several mainstream server processors.

Ventana claims customers using Ventana CPU and I/O modules to design SoCs can shorten development time by two years and save approximately $75 million in R&D costs. Although the software ecosystem is still maturing and Veyron V1 is not a general-purpose server CPU, the performance profile suggests it can address roughly half of typical data center CPU workloads such as in-memory databases, application hosting, storage servers, load balancing, caching, content delivery, and streaming.

RISC-V progress in the Chinese market and automotive certification

In March 2023, Chinese company Suanneng launched the SOPHON SG2042, a 64-core RISC-V server processor based on the Pingtouge XuanTie high-performance C920 RISC-V core, running at up to 2 GHz with a 9–12 stage pipeline, out-of-order execution, and a 64 MB shared L3 cache. In August 2023 Suanneng disclosed the next-generation SOPHON SG2044 with upgraded DDR bandwidth and PCIe support.

In the automotive sector, SiFive introduced the Automotive series RISC-V core IP optimized for infotainment, cockpit, connectivity, ADAS, and electrification, including the E6-A, X280-A, and S7-A cores. Multiple automotive component suppliers and tool vendors have adopted SiFive Automotive RISC-V cores, including Ashling, Cadence, Canonical, Elektrobit, Green Hills, IAR Systems, iSystem AG, Lauterbach, Renesas, Resiltech, Segger, Siemens, Solid Sands, Synopsys, SYSGO, TASKING, and WITTENSTEIN.

Chinese CPU IP startup Andes Technology's NA series CPU IP (NA900 and NA300) obtained ISO 26262 ASIL D certification in July 2023. Andes' CEO said this milestone is significant for the company and for RISC-V adoption in automotive functional safety applications.

Conclusion

Both automotive electronics and data center servers are driving high-end RISC-V adoption. Automotive requires strict safety certification and deep hardware-software coupling for product differentiation, which favors RISC-V customizability. Servers offer a focused, high-volume market where cloud-oriented architectural optimizations and custom extensions yield economic and energy advantages. Given lower regulatory barriers and the scale of cloud workloads, server deployment may reach volume more quickly, while automotive deployment continues to advance through safety certification and vendor adoption.

ALLPCB

ALLPCB