Overview

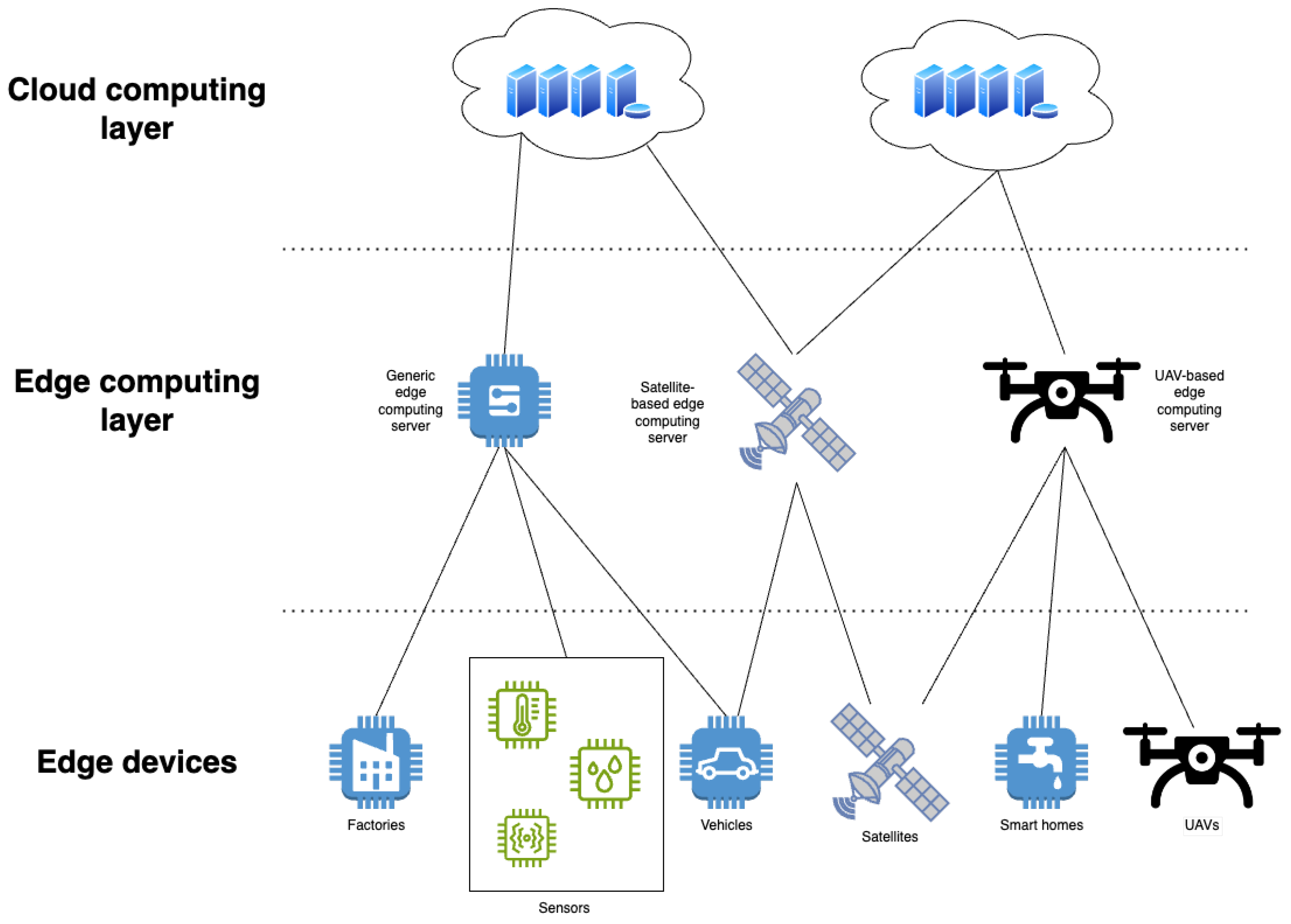

At its 2023 investor meeting, Nvidia presented a revised GPU roadmap that shortens the development cadence from two years to one year. The roadmap indicates H200 and B100 GPUs arriving in 2024 and an X100 GPU expected in 2025. The strategic core is a unified "One Architecture" that supports model training and deployment across data centers and edge devices, and across x86 and Arm hardware. The planned solutions target both hyperscale data center training and enterprise edge computing.

Product Cadence and Positioning

The shift from a two-year to a one-year update cycle reflects faster product development and quicker market response. The roadmap covers both training and inference workloads, with an emphasis on inference and on supporting both x86 and Arm ecosystems. Market positioning addresses hyperscale cloud providers and enterprise users. Nvidia combines GPU, CPU, and DPU offerings and integrates these with NVLink, NVSwitch, NVLink C2C interconnects and CUDA to form a cohesive hardware and software ecosystem.

Compute Architecture and SuperChip Concept

The architecture emphasizes integration of training and inference functions while placing more weight on inference. Nvidia pursues two platform routes centered on the GPU: ARM and x86. The Grace CPU appears within the Grace+GPU SuperChip roadmap rather than as a separate CPU-only trajectory. Grace CPUs are expected to evolve at a slower cadence and to be combined with GPUs into next-generation SuperChips. CPUs are more cost sensitive and generally follow a Moore-or-system-Moore rhythm, roughly doubling performance every two years, whereas GPU performance has been pushed to increase at a much faster pace, historically approaching annual performance gains. This divergence in cadence motivates the SuperChip and supernode concepts.

Interconnect and SuperNode Architecture

Nvidia continues to use the SuperChip architecture, where NVLink-C2C and NVLink remain central interconnect technologies. NVLink-C2C is used to assemble GH200, GB200, and GX200 SuperChips. Further, pairs of these SuperChips can be connected back-to-back using NVLink to form GH200NVL, GB200NVL, and GX200NVL modules. NVLink networks can form supernodes, and larger AI clusters can be formed over InfiniBand or Ethernet fabrics.

Switch Chip Roadmap and SerDes Evolution

Nvidia maintains two open switch chip paths based on InfiniBand and Ethernet, targeting different market segments. InfiniBand targets high-performance AI factory use cases, while Ethernet targets cloud AIGC environments. The roadmap indicates generational SerDes speed increases; 2024 is expected to see 800G switch interfaces based on 100G SerDes, and 2025 may introduce 1.6T interfaces based on 200G SerDes. An 800G-capable Spectrum-4 corresponds to roughly 51.2T switching capacity, while a 1.6T-capable Spectrum-5 could approach 102.4T. Long-term trends suggest SerDes rates tend to double roughly every 3 to 4 years, while switch capacity doubles roughly every 2 years. The public record currently shows Quantum-2 as a 400G-interface, 25.6T chip announced in 2021. The roadmap does not explicitly list NVSwitch 4.0 or NVLink 5.0, though some analyses predict 224G SerDes may appear first on NVLink and NVSwitch. As proprietary technologies, NVLink and NVSwitch can follow a more flexible schedule than standardized ecosystems.

SmartNICs, DPUs, and Network Bandwidth Balance

The next-generation SmartNIC and DPU targets include ConnectX-8 and BlueField-4 aiming for 800G. The roadmap alignment between SmartNIC/DPU and 1.6T switches is less clear. NVLink and NVSwitch may reach higher performance earlier due to their proprietary nature. ConnectX SmartNICs combined with InfiniBand enable larger NVLink-based supernode clusters, while BlueField DPUs are oriented to cloud data center environments over Ethernet. Bandwidth comparisons highlight a notable gap between traditional network interfaces and bus-domain interconnects: for example, an H00 GPU's PCIe bandwidth for connecting SmartNICs and DPUs is 128 GB/s, which can at most support a 400G InfiniBand or Ethernet interface after PCIe-to-Ethernet conversion, whereas NVLink bidirectional bandwidth can be 900 GB/s or 3.6 Tbps. This yields an approximate 1:9 bandwidth ratio between traditional network domains and NVLink-like bus domains. Although SmartNIC and DPU bandwidth growth lags the bus-domain network increases, they must still evolve in step with large switch capacities. Their evolution is also constrained by the maturity of interoperability standards developed by IBTA and IEEE 802.3.

Optical and Electrical Interconnect Technologies

Interconnect technology is critical to scaling future computing systems. Nvidia is developing LinkX optical-electrical interconnects, including pluggable optics with traditional DSP engines, linear pluggable optics (LPO), DAC cables, redriven active copper cables, and co-packaged optics. As supernodes and cluster networks scale, interconnect design must address bandwidth, latency, power, reliability, and cost trade-offs.

Competitive Landscape and Strategic Drivers

Competition from Google, Meta, AMD, Microsoft, and Amazon has intensified, with these companies advancing both hardware and software efforts to challenge Nvidia's position. This competitive pressure likely influences a more aggressive technical roadmap. Nvidia's strategy includes annual GPU updates and the introduction of technologies such as HBM3E memory, PCIe 6.0 and PCIe 7.0 support, NVLink evolution, 224G SerDes, and 1.6T interfaces. Success in these areas would strengthen Nvidia's competitive standing.

Constraints, Supply Chain, and Financial Position

Hardware innovation is bounded by first principles and physical limits. Analysis of process nodes, advanced packaging, memory, and interconnect yields plausible technical paths. Non-technical factors such as supply chain control or capacity bottlenecks for components like HBM or advanced CoWoS packaging can influence the pace of deployment. Nvidia's financial results show strong cash flow that can affect supply chain dynamics: fiscal Q4 2023 revenue was $7.64 billion, up 53% year over year, and fiscal year revenue was $26.91 billion, up 61%. Q4 data center revenue was $3.26 billion, up 71% year over year; full fiscal year data center revenue was $10.61 billion, up 58% year over year. External events can also cause disruptions; for example, geopolitical events have affected planned public events and product announcements. Nvidia's networking unit originated from Mellanox, which has operations in Israel.

Analytical Scope and Assumptions

This analysis is grounded in first-principles technical reasoning and does not incorporate economic measures such as deliberate supply-chain interventions or unpredictable black-swan events. Such factors could significantly affect timing or product availability, but they are treated as external uncertainties. The evaluation focuses on likely technical trajectories over a two-to-three-year horizon through 2025. Conclusions should be adjusted if key assumptions change.

Nvidia, AMD, and Other Industry Approaches

Nvidia's roadmap covers compute and networking, including chips, SuperChips, supernode networks, and cluster fabrics. AMD follows with a strong focus on CPU and GPU compute and advanced packaging with chiplet integration. Unlike Nvidia's SuperChip concept, AMD integrates CPU and GPU dies using advanced packaging and relies on its Infinity Fabric interface for coherence. GPU-CPU links still use PCIe for certain connections. AMD is developing its own switch chip, XSwitch, and the next-generation MI450 accelerator will use a new interconnect architecture intended to compete with NVSwitch.

Network Vendors and Alternative Architectures

Broadcom focuses on networking silicon, offering InfiniBand-like Jericho3-AI+ solutions for supernode networks and Tomahawk and Trident series for cluster fabrics. Recent Broadcom devices include programmable Trident 5-X12 features that apply neural-network inference to traffic classification and congestion control. Other players such as Cerebras and the Tesla Dojo effort pursue wafer-scale or deep custom packaging routes for highly specialized accelerated systems.

ALLPCB

ALLPCB