Overview

As integration increases, digital circuits become more complex. Few systems operate on a single clock; multiple clock domains are common, and clocks may be synchronous or asynchronous. When a signal channel crosses between asynchronous clock domains, a clock domain crossing (CDC) issue can occur.

If CLKA and CLKB have no fixed phase relationship and are asynchronous. The left portion of the design belongs to clock domain CLKA, and the right portion belongs to clock domain CLKB. The signal DA moves from CLKA into CLKB, which is a CDC path.

CDC challenges

In frontend RTL design, common problems arise when asynchronous control and data signals are not handled correctly. Improper handling can result in metastability and functional failures.

SpyGlass overview

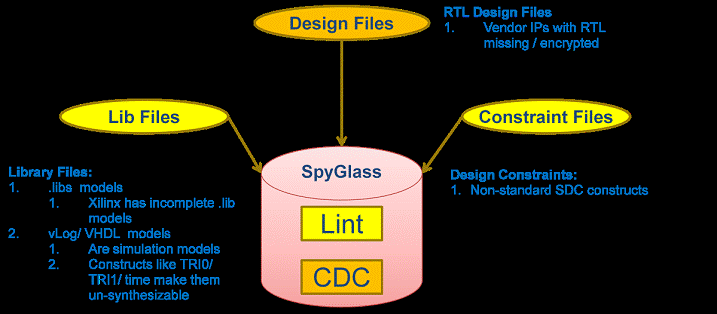

SpyGlass is an RTL sign-off tool that includes multiple analysis modules. Key modules include lint, CDC (clock-domain crossing), LP (low power), Constraint (timing constraints), and DFT (design for testability).

SpyGlass CDC analysis

SpyGlass CDC analysis identifies potential CDC issues in the design. Compared with writing directed simulation tests to find CDC problems, a formal CDC check methodology can detect issues earlier, more completely, and more quickly. Typical capabilities include:

- Managing designs with multiple clock domains

- Systematically identifying CDC issues

- Checking and reporting asynchronous signals such as clocks and resets

Comparison with static timing analysis (STA)

- STA is not well suited for asynchronous interfaces and is mainly for synchronous module timing analysis

- CDC paths often need to be annotated as false paths for STA

- STA-based CDC analysis is generally more meaningful at the netlist level in later design stages

Comparison with functional simulation

- Black-box tests are difficult to exhaustively cover

- White-box tests require assertions

- Covering all CDC test branches is challenging, so simulation typically finds only a subset of issues

- CDC problems are often discovered late in the design flow when relying on simulation alone

When CDC checking is useful

When a SoC design involves many clock domains, multiple third-party IPs, and teams with varying experience levels, static CDC checking can help improve RTL quality and reduce integration risk.

Block-level vs SoC integration goals

CDC goals differ between block-level design and SoC integration. Block-level checks focus on internal module correctness and should be completed before module delivery. SoC integration focuses on CDC issues at module interfaces.

ALLPCB

ALLPCB