01 Overview

SoC (system on chip) integrates a CPU, various memories, bus systems, dedicated modules, and multiple I/O interfaces on a single chip. Due to the large scale of SoCs and the diversity of internal module types and sources, DFT for SoCs faces multiple challenges.

2. Test Issues Related to SoC

3. Comprehensive SoC Testing

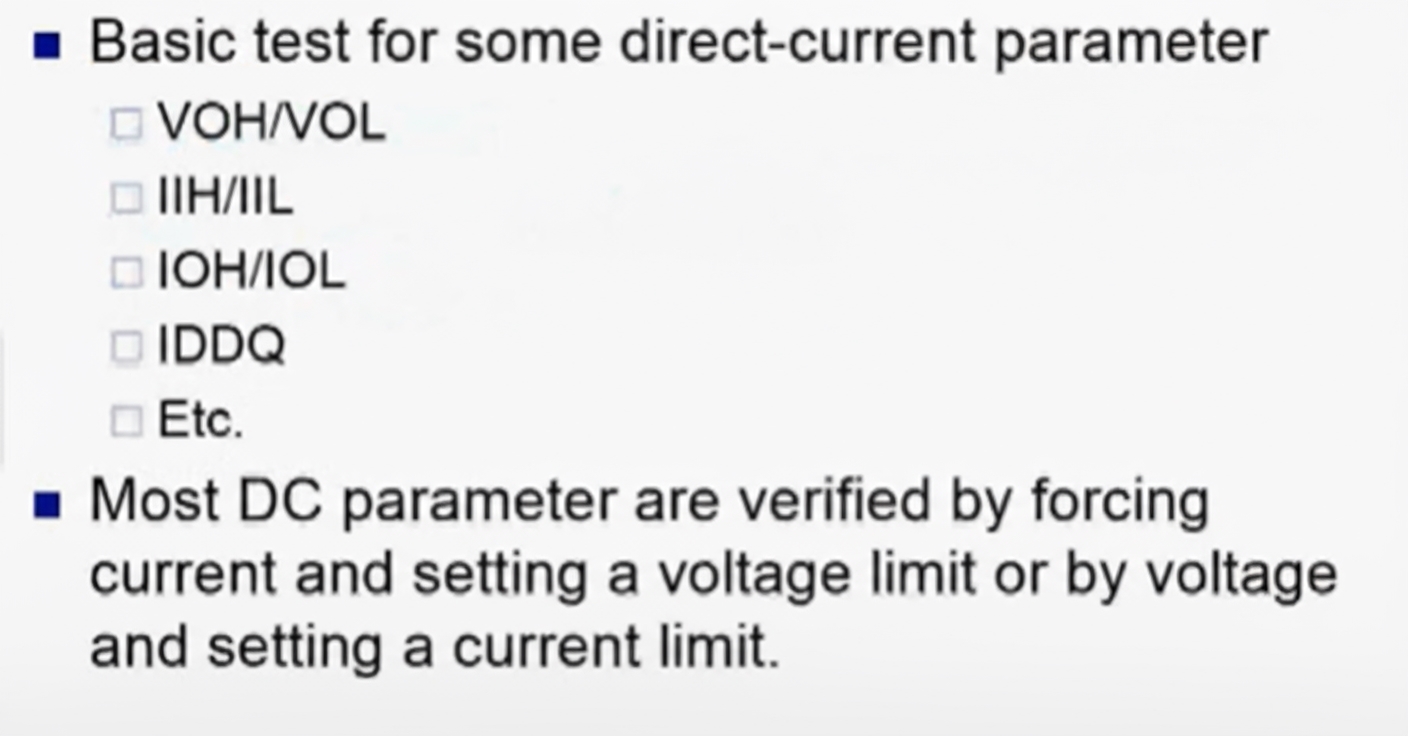

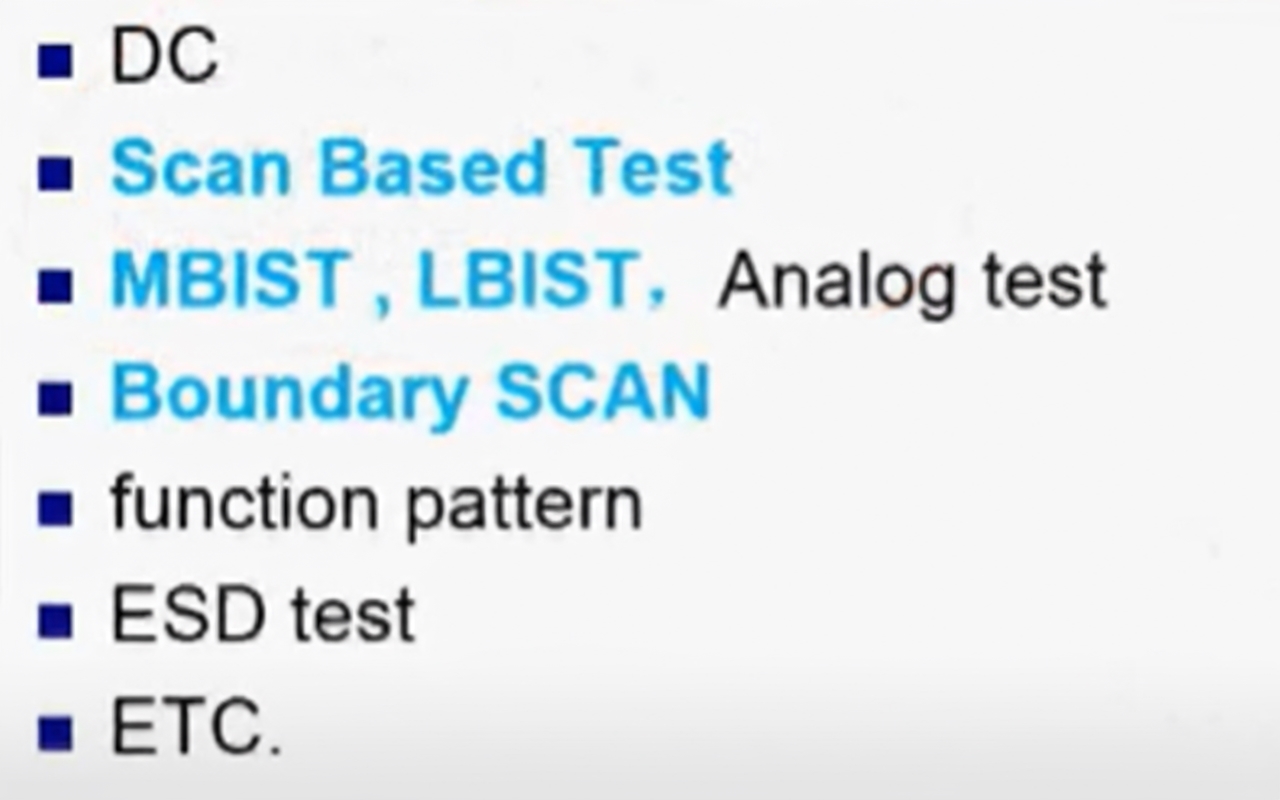

Testing is prioritized by risk; DC tests are generally performed first.

DC test - DC parameter testing

Scan-based Test

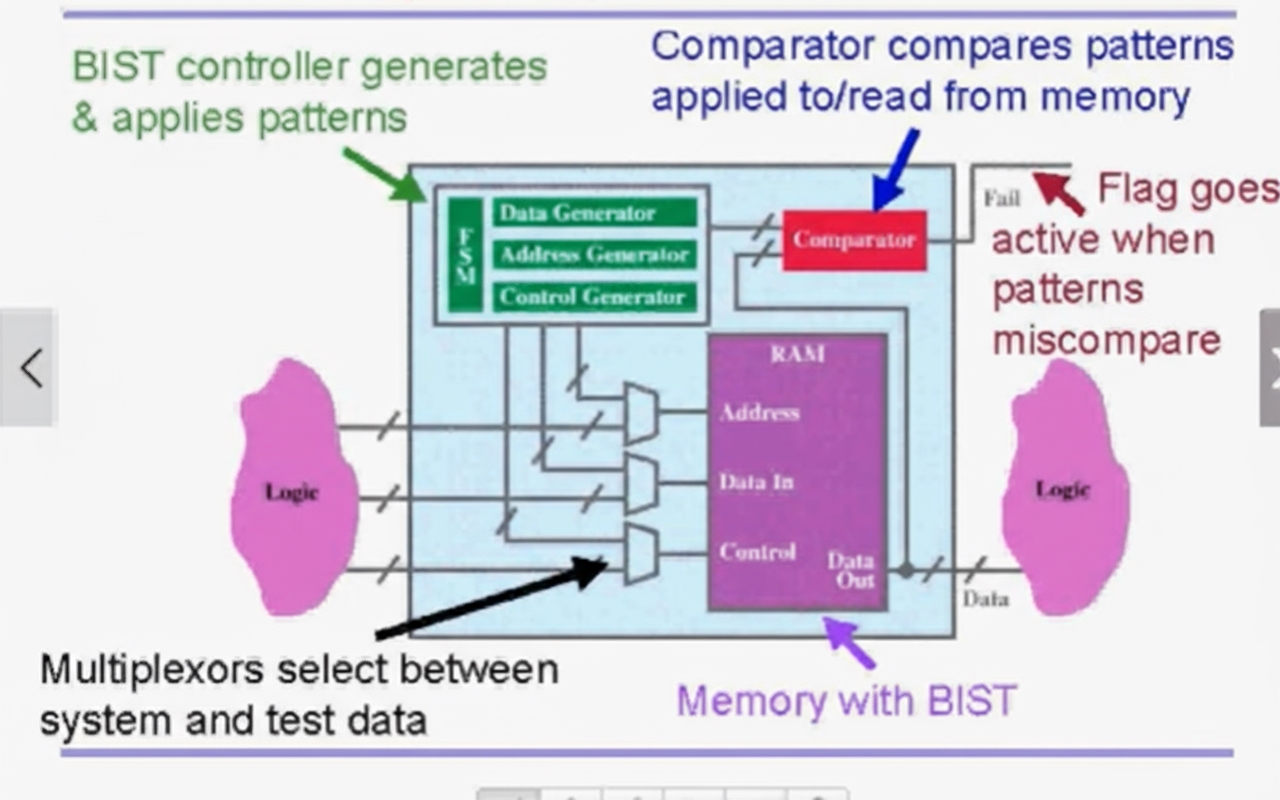

BIST - Built-In Self-Test

BIST Types and Applications

Logic BIST: Advantages and Disadvantages

Boundary Scan — JTAG

There are three different protocols with different functions and support. Boundary scan verifies connectivity between the chip and pads.

DFT Position in the IC Design Flow

DFT interacts to varying degrees with the four areas shown on the left. Most teams include DFT within the overall design flow.

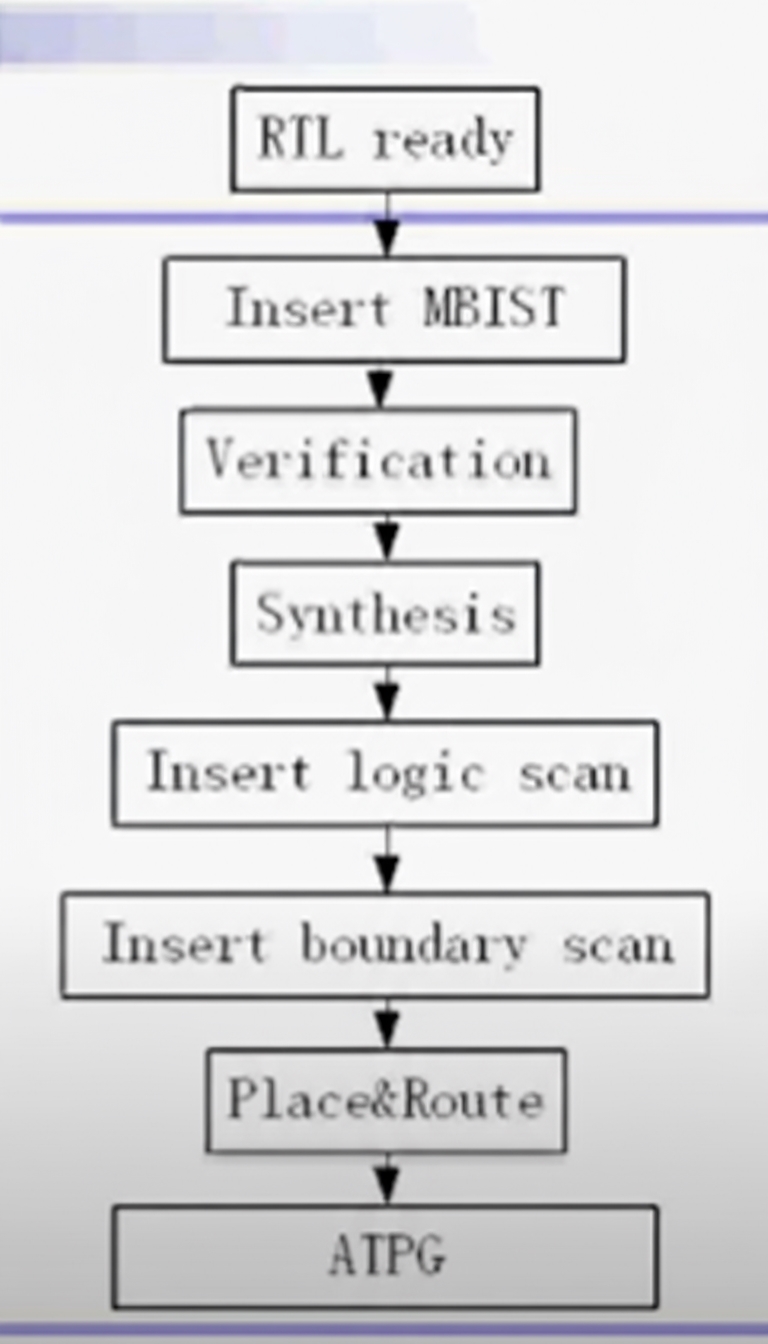

DFT Flow and Tasks at Each Step

1. A DFT Reference Flow

The sequence of each DFT step can be changed.

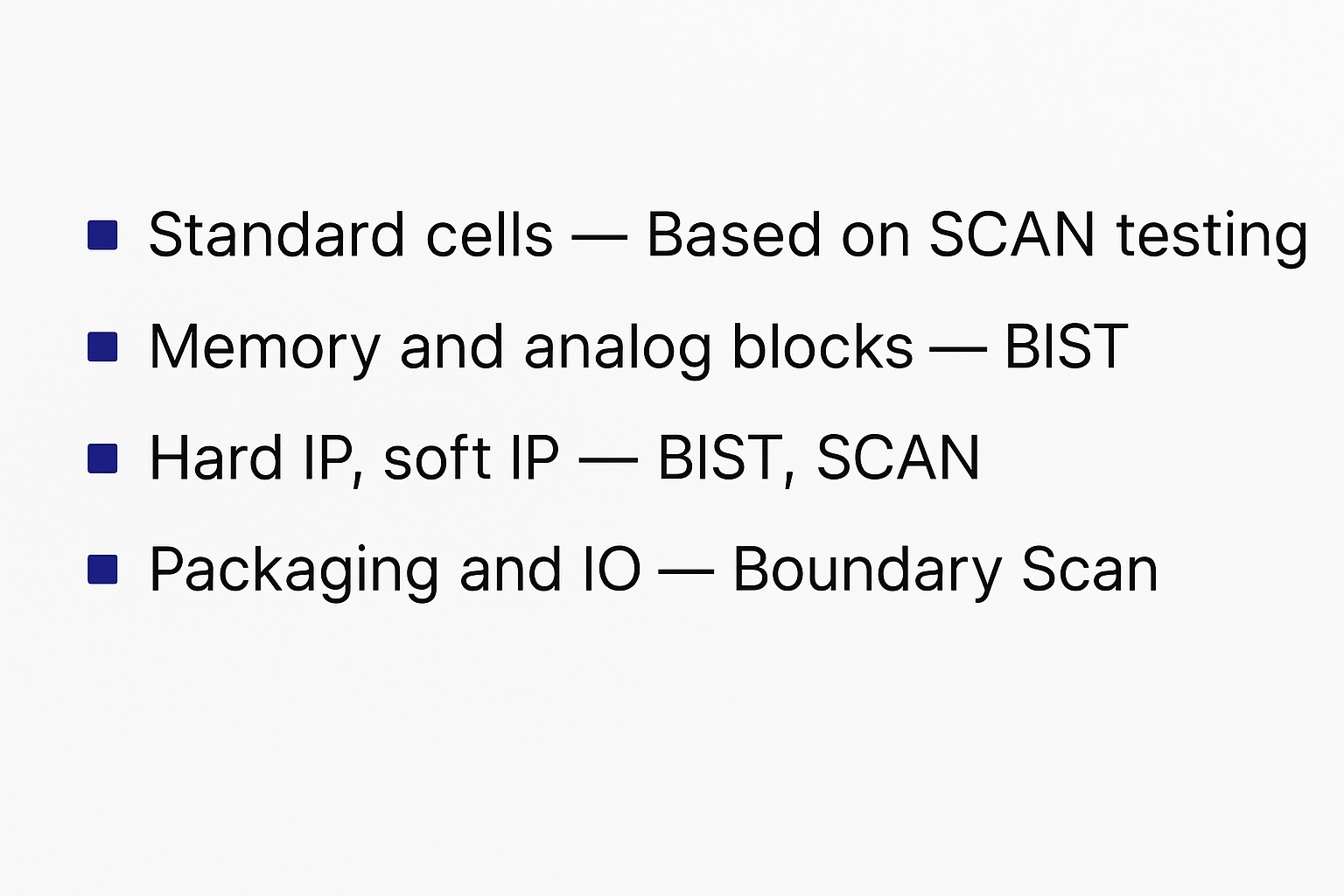

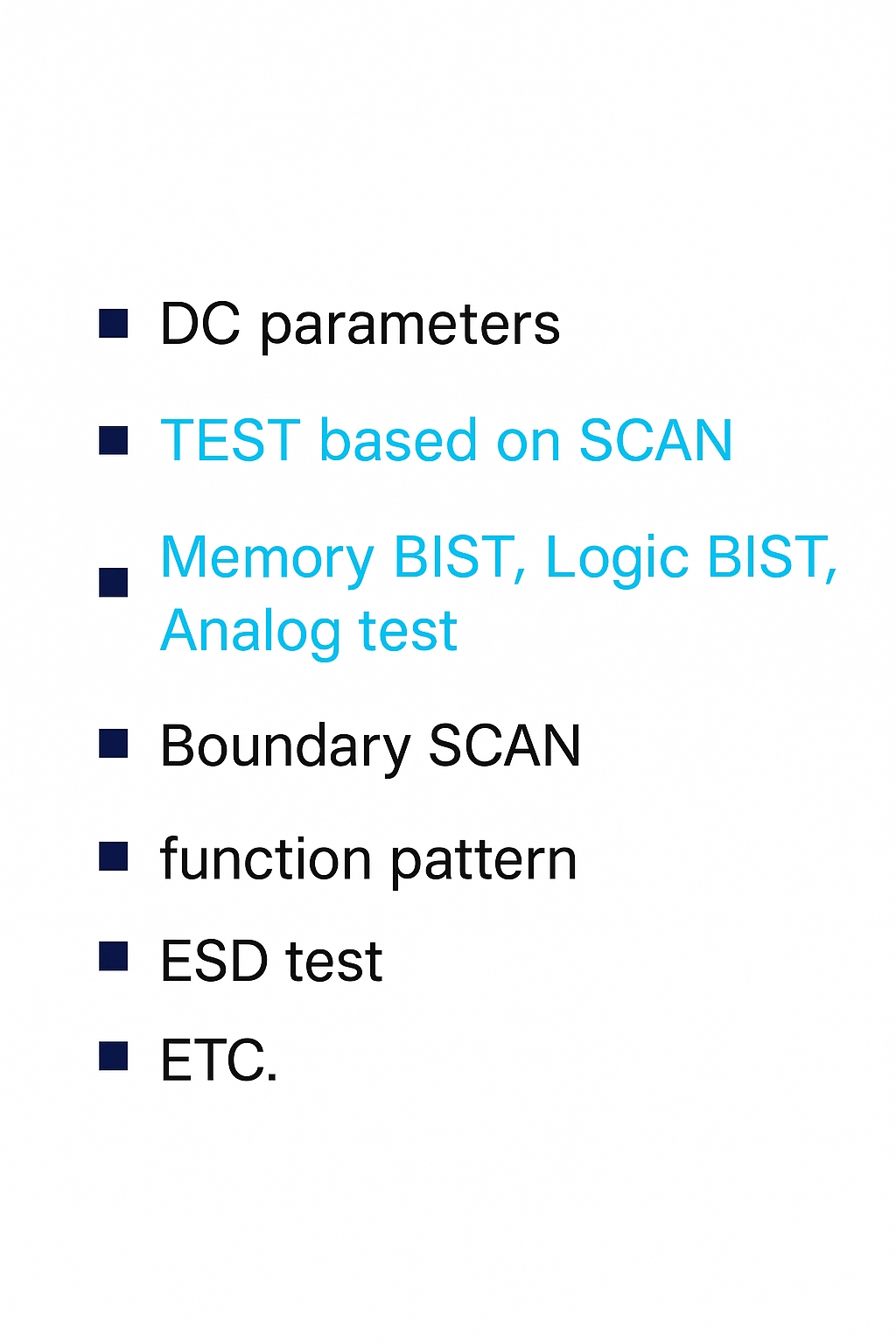

Test Items — Theory and Tool Implementation

The highlighted items are key DFT focus areas.

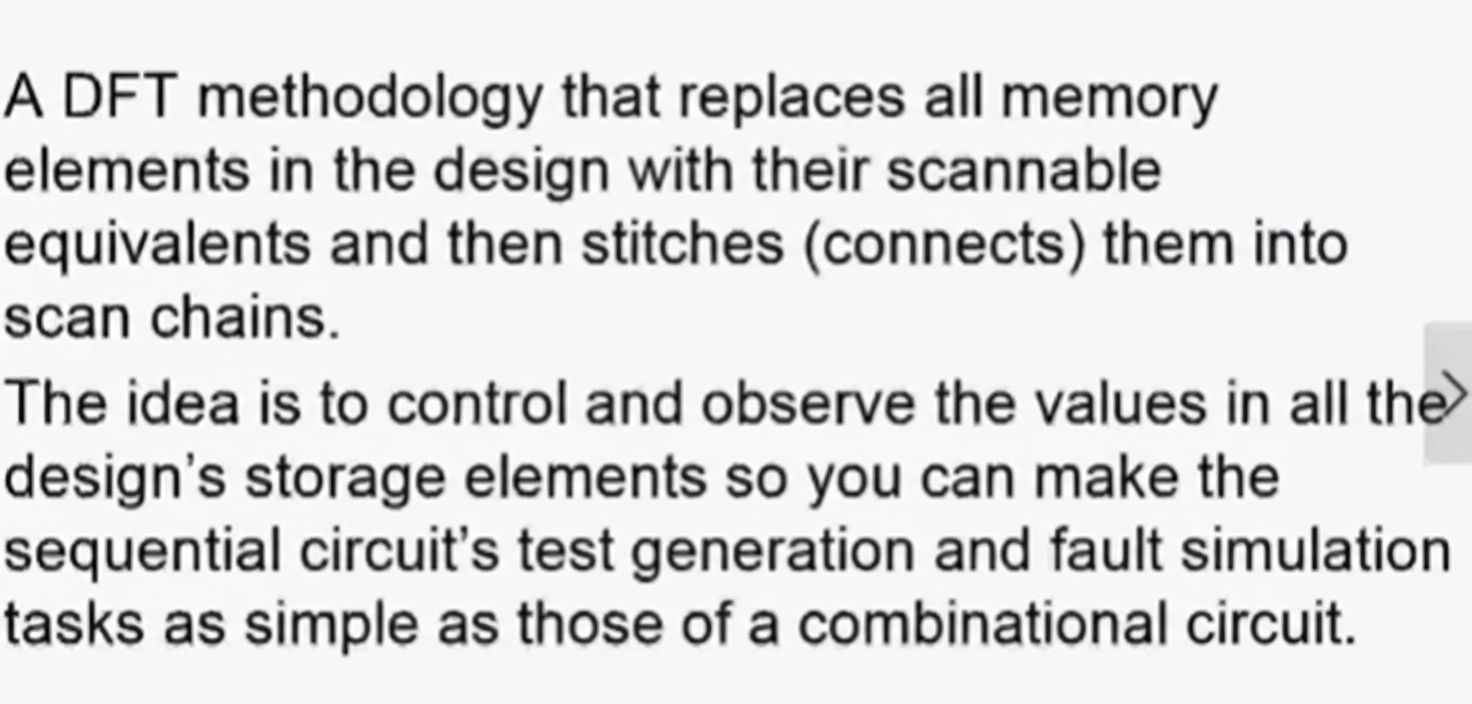

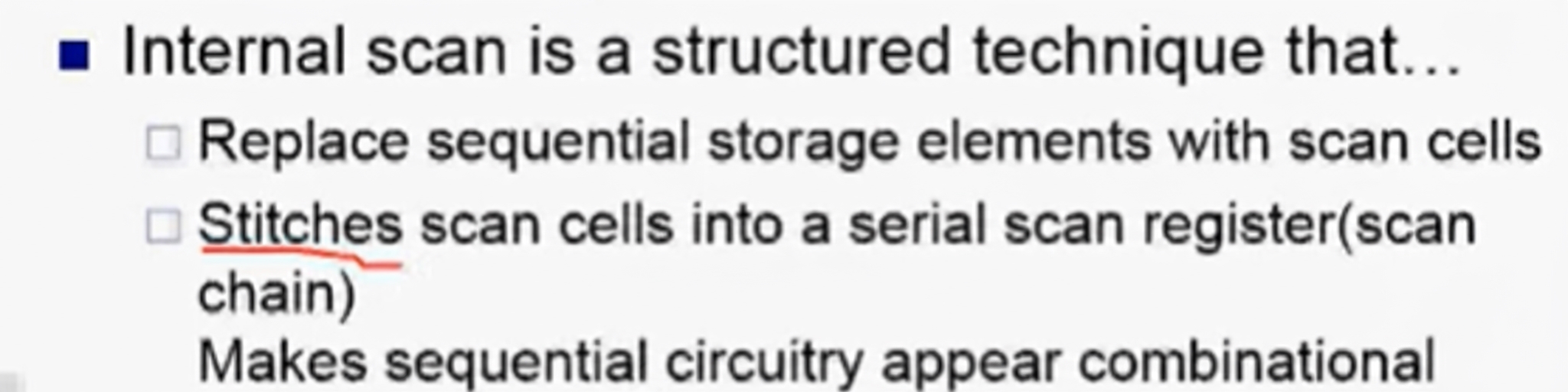

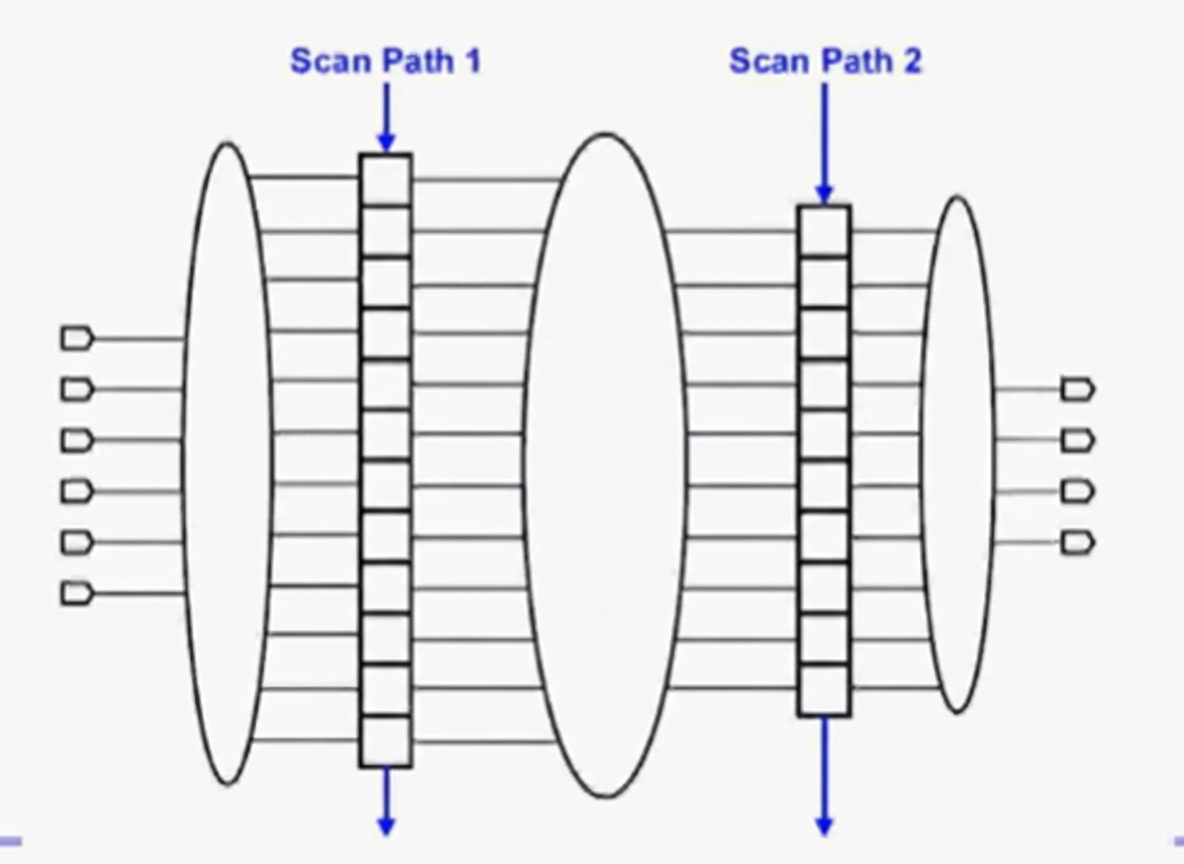

2. Scan-Based Test

There is also latch-based testing, but it is not mainstream.

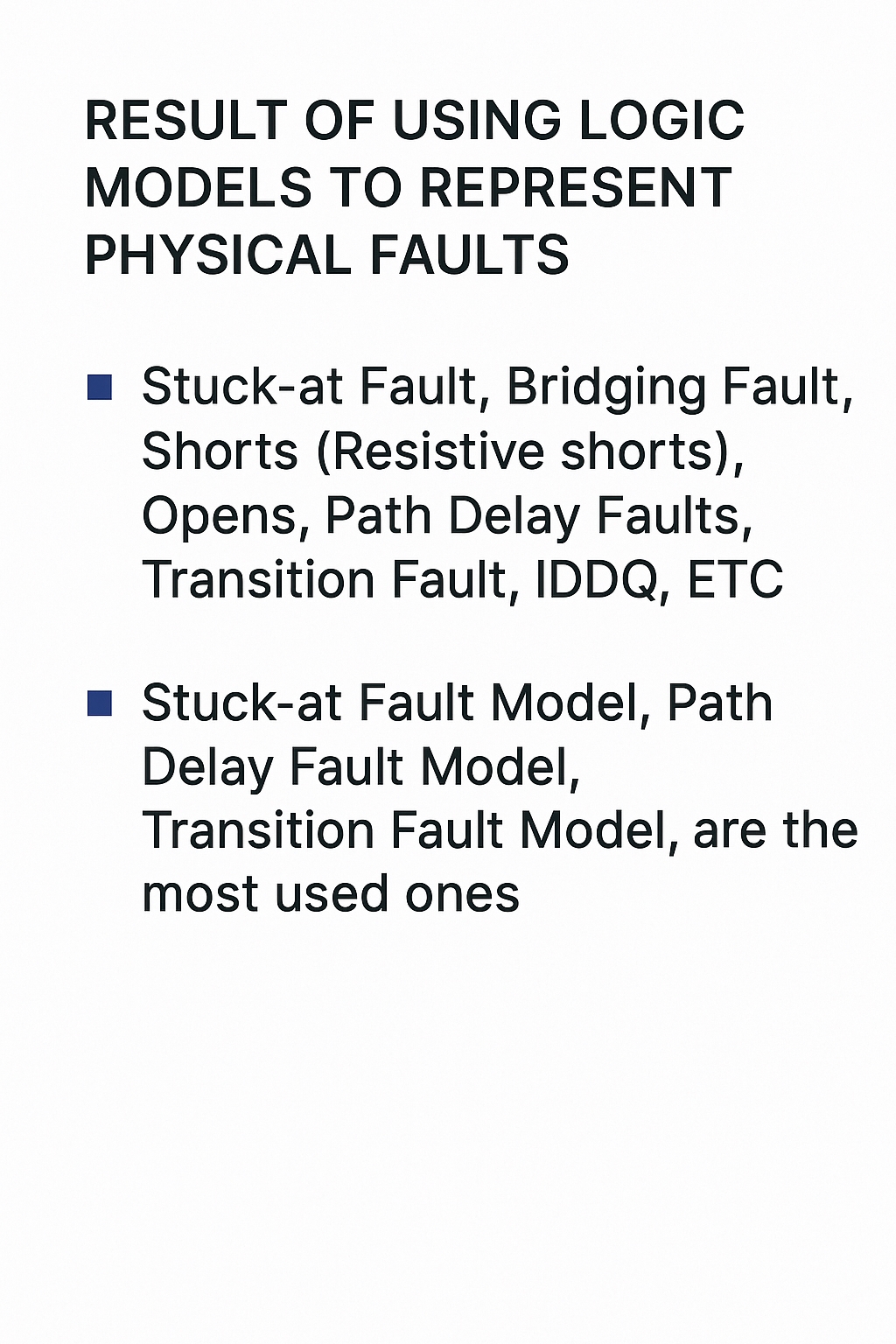

3. Fault Models vs. Defects

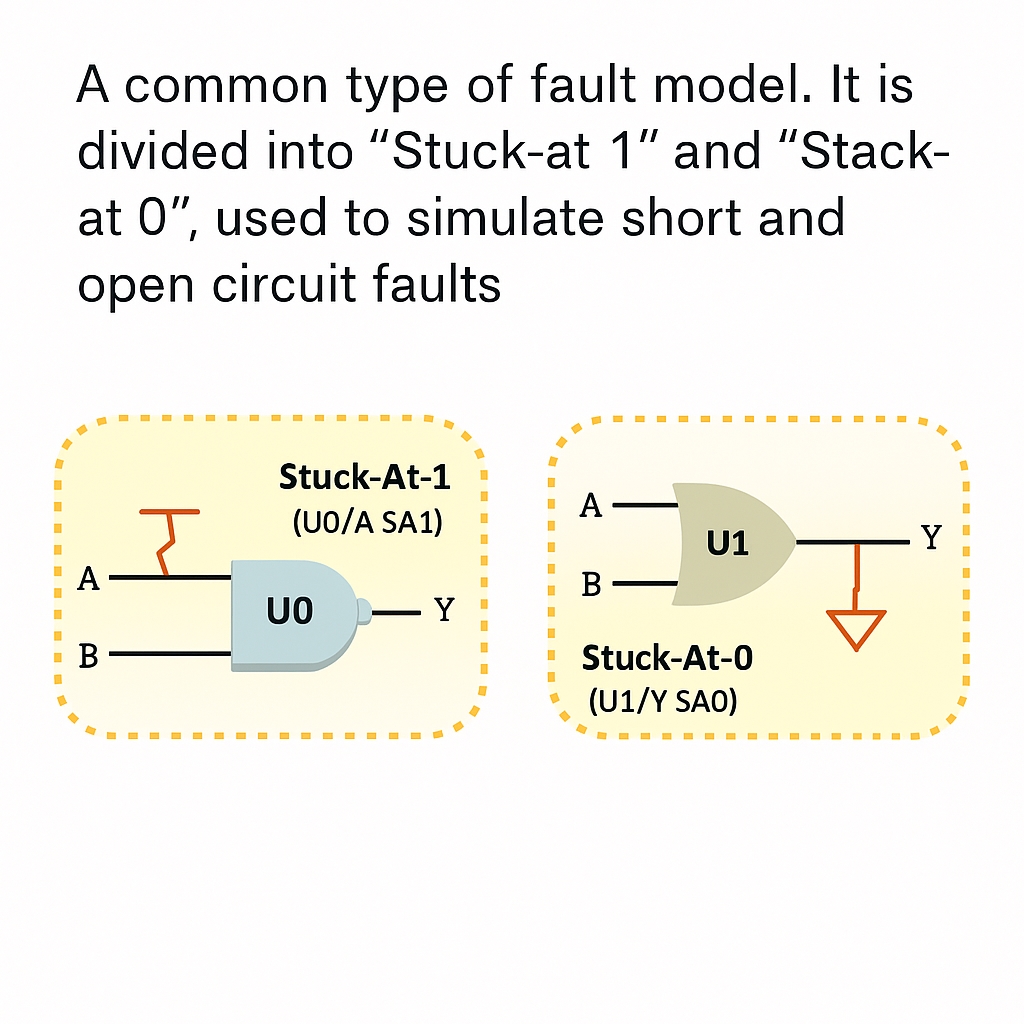

4. Stuck-at Fault — For Low-Speed Testing

5. At-Speed Fault — For At-Speed Testing

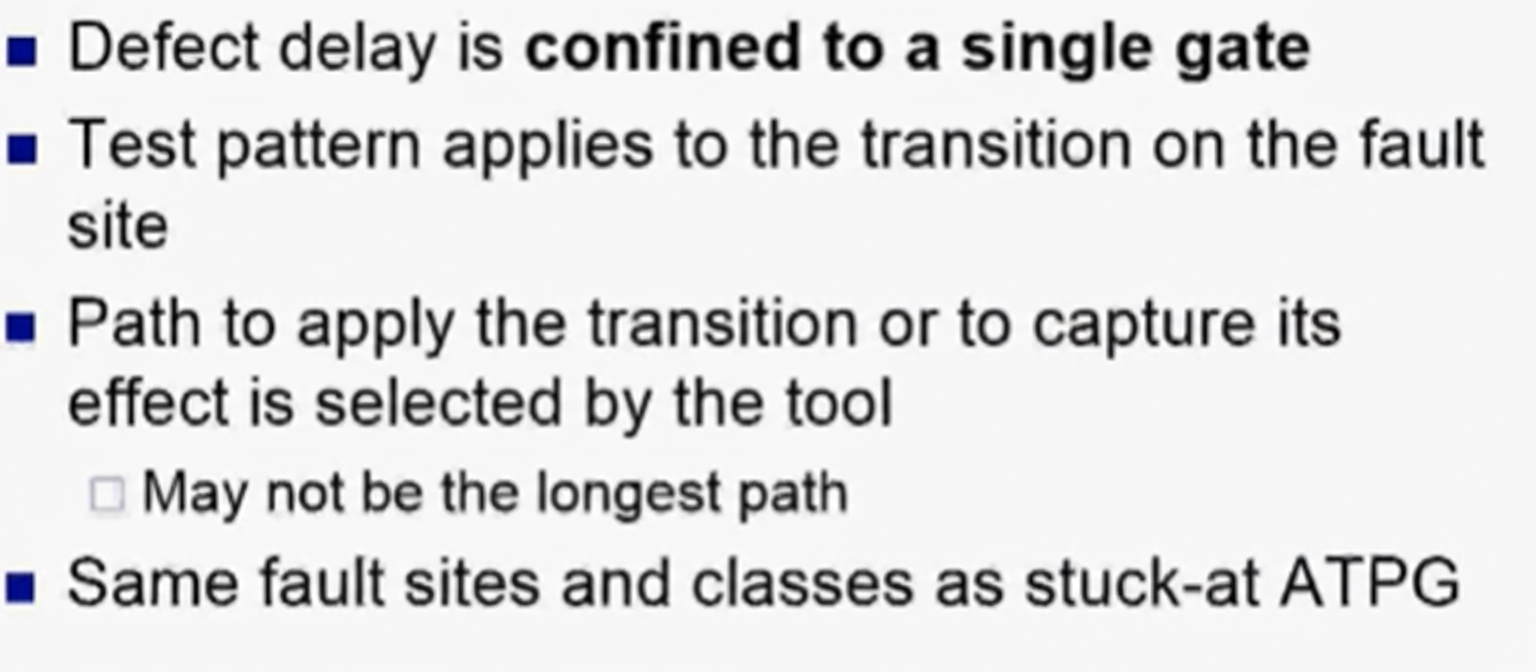

6. Transition Delay Fault Model

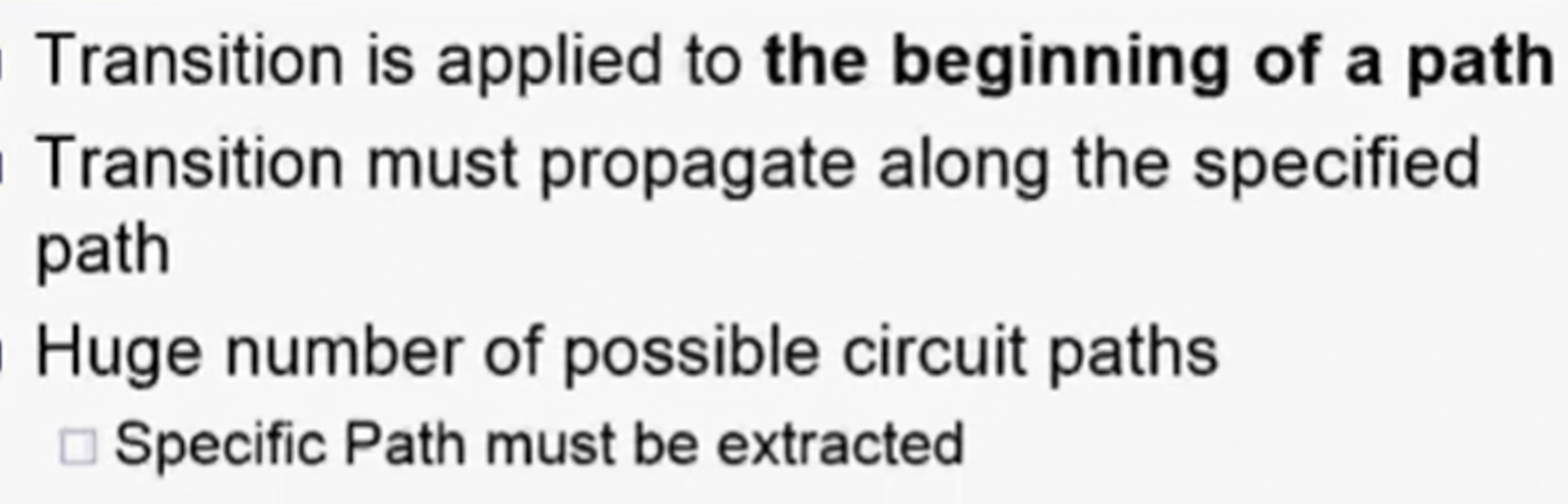

7. Path Delay Model

8. D Algorithm

9. How Scan Test Works

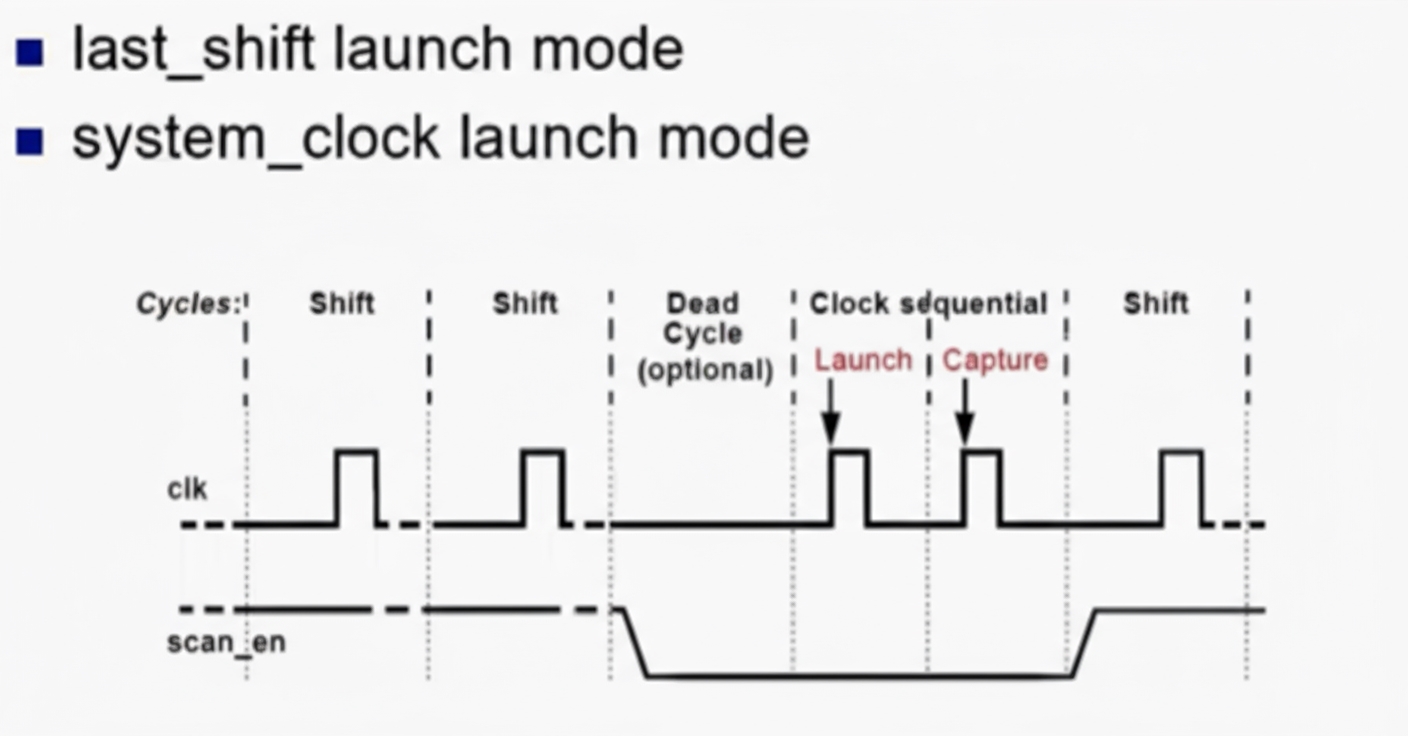

10. Transition Launch Mode

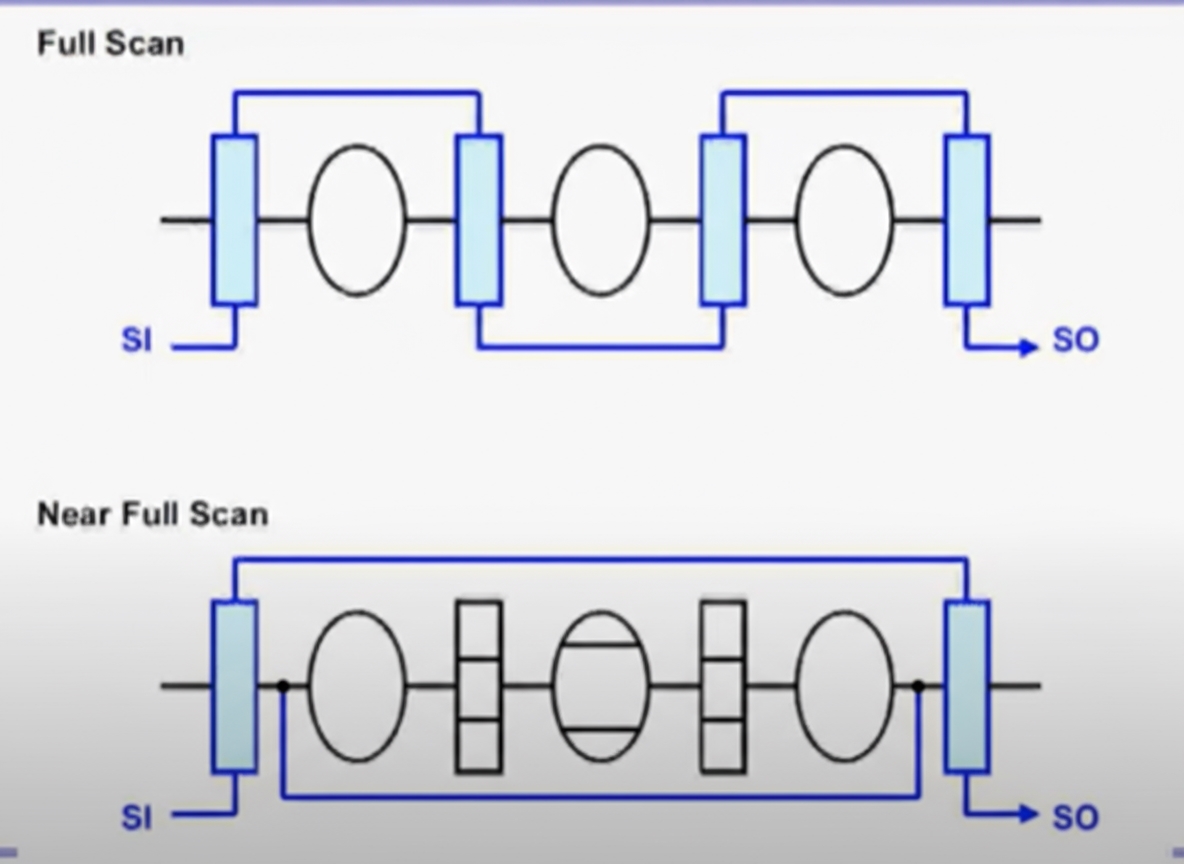

11. Full Scan & Partial Scan

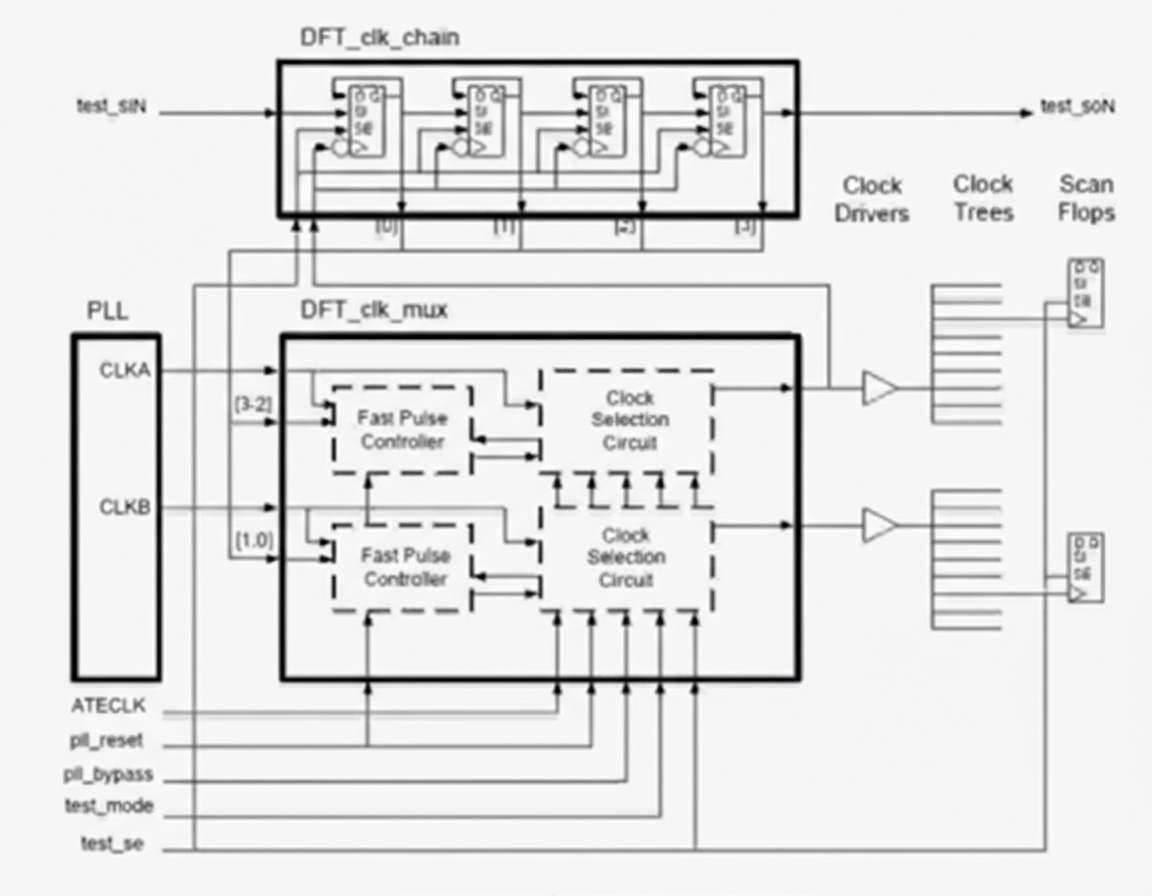

12. At-Speed Test & OCC

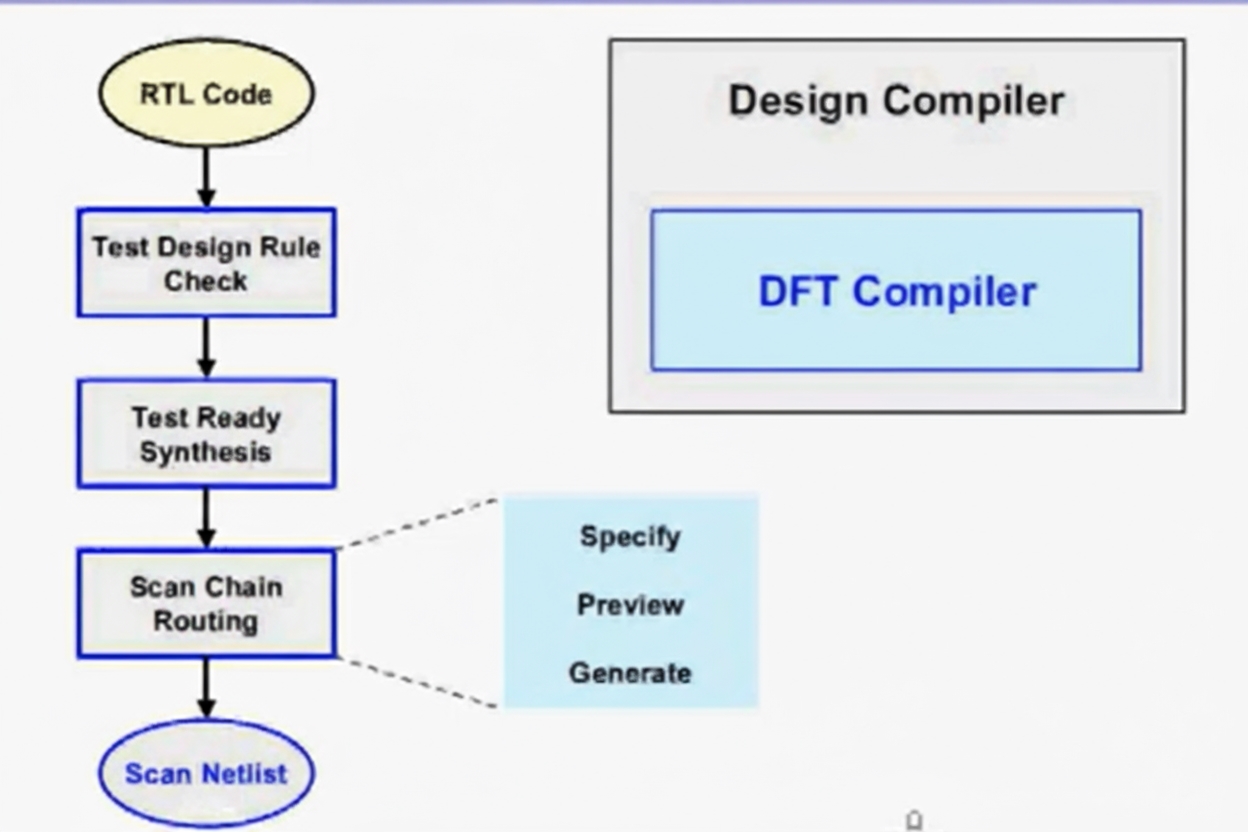

Scan chain synthesis flow — added after synthesis.

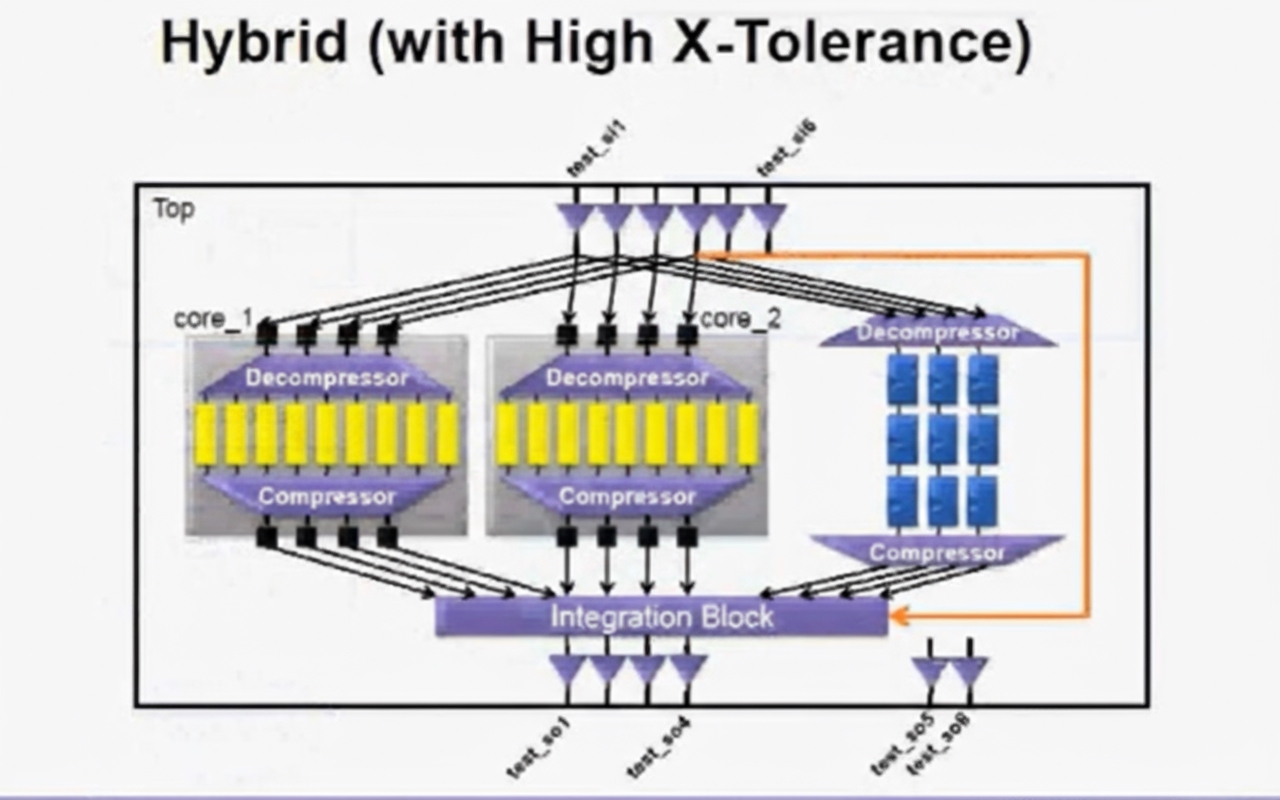

Compression

Used to reduce test time.

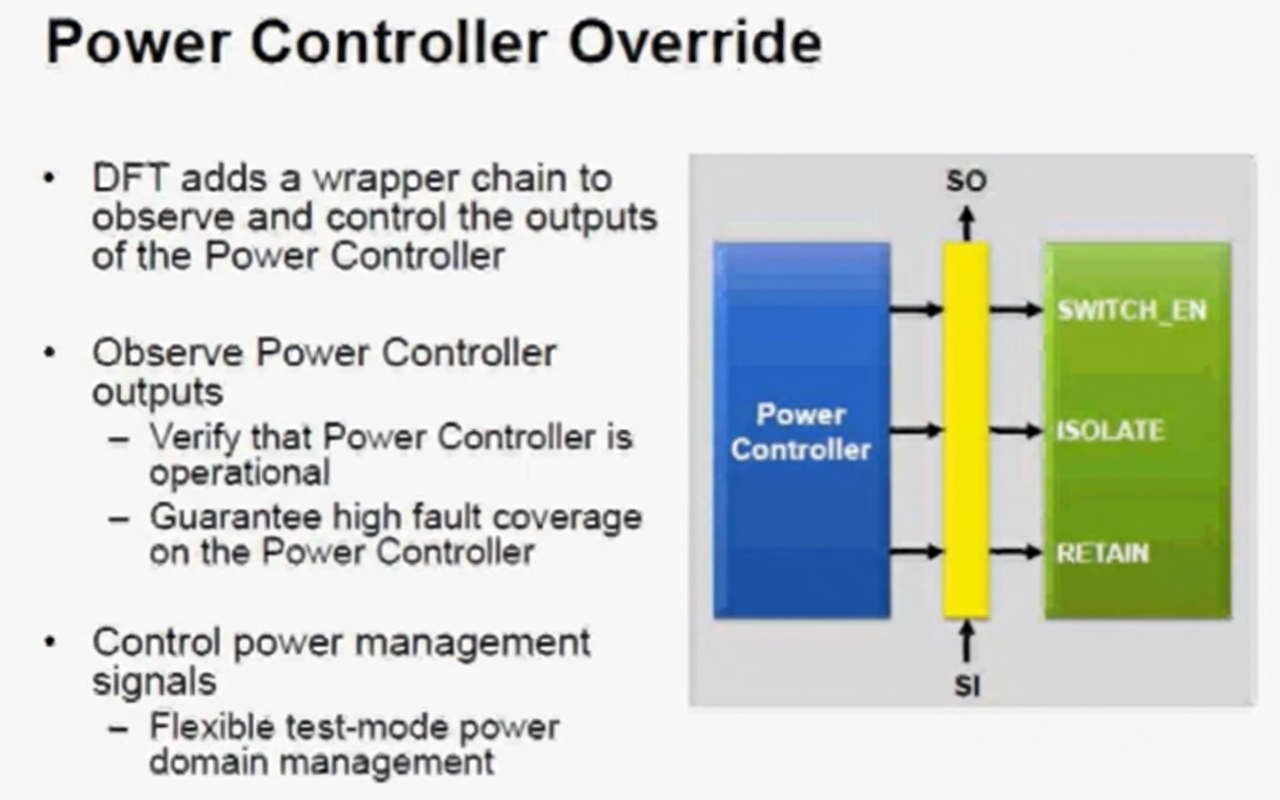

13. Multi-Power DFT

Power considerations: functional domains may use multiple voltage thresholds, whereas DFT typically uses a single test voltage. For very large chips with multiple voltage domains, testing across all domain voltages is rare but possible.

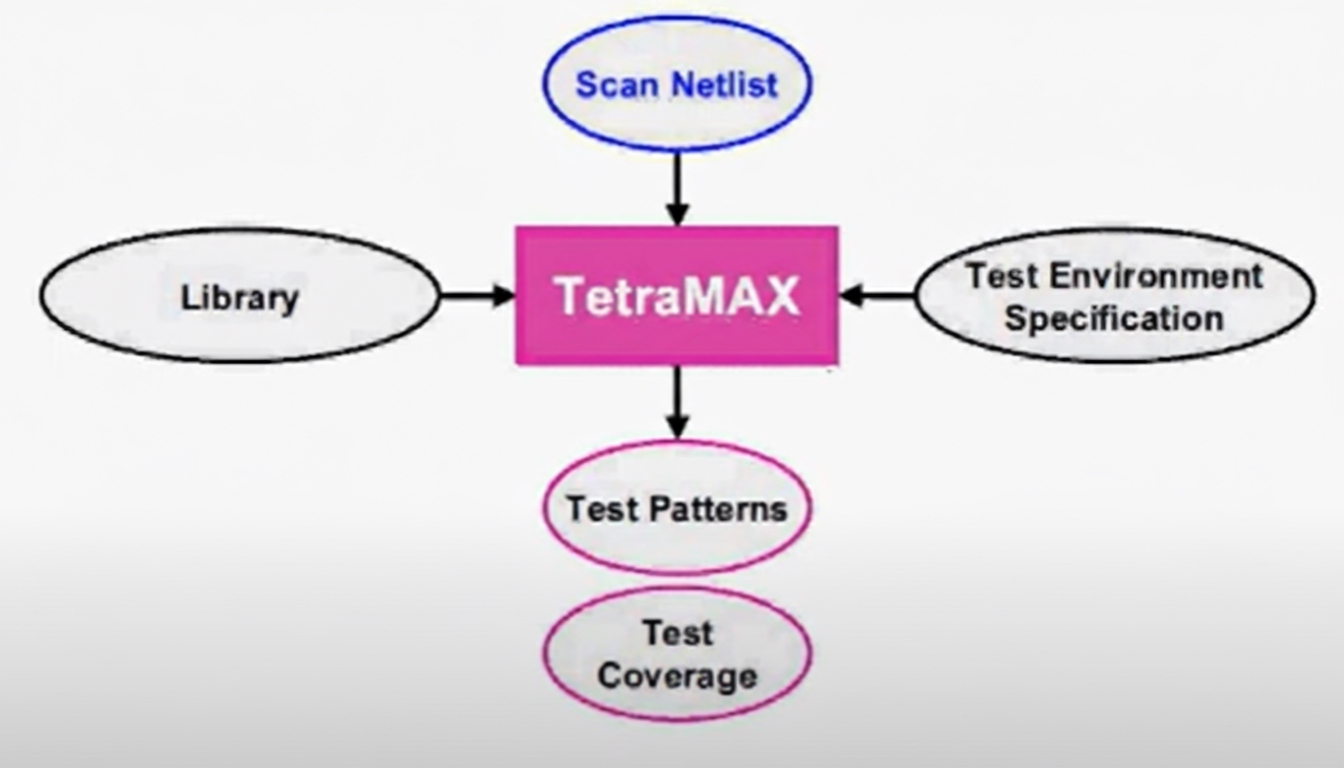

ATPG — Automatic Test Pattern Generation

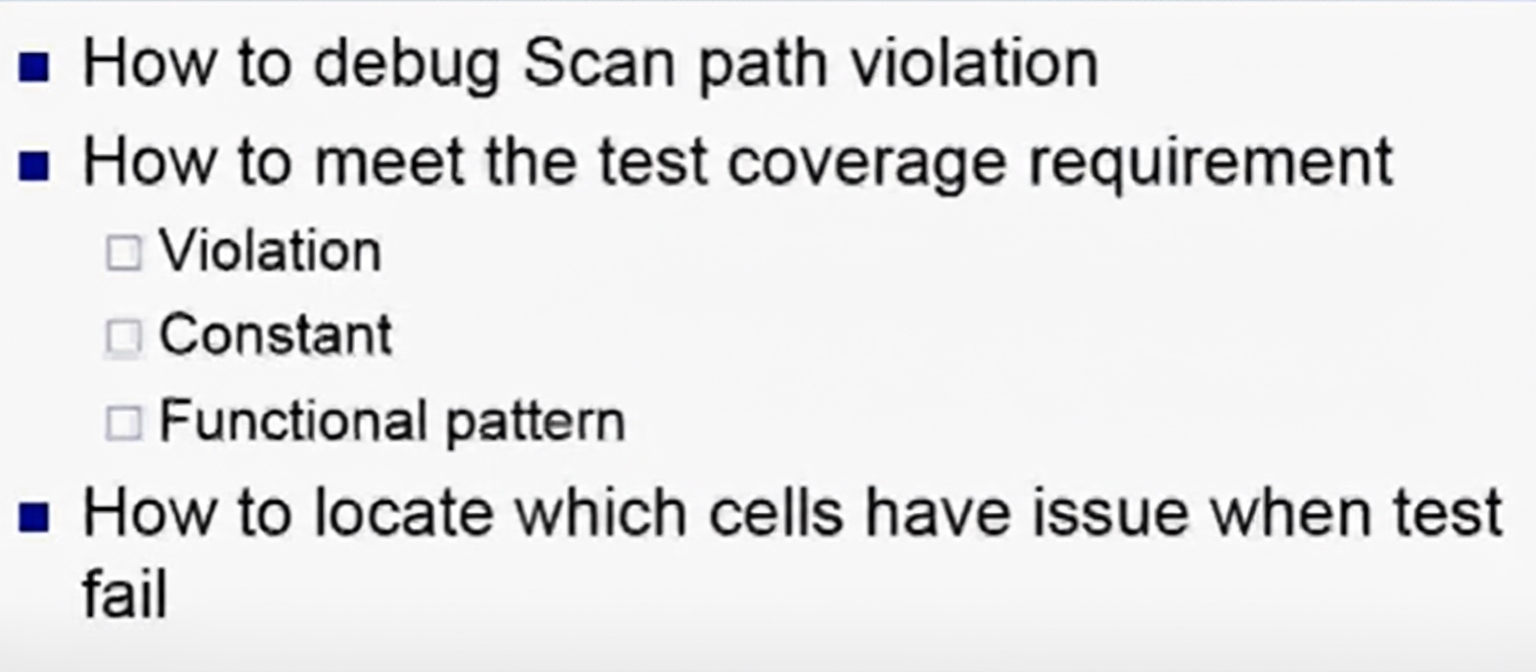

ATPG Focus

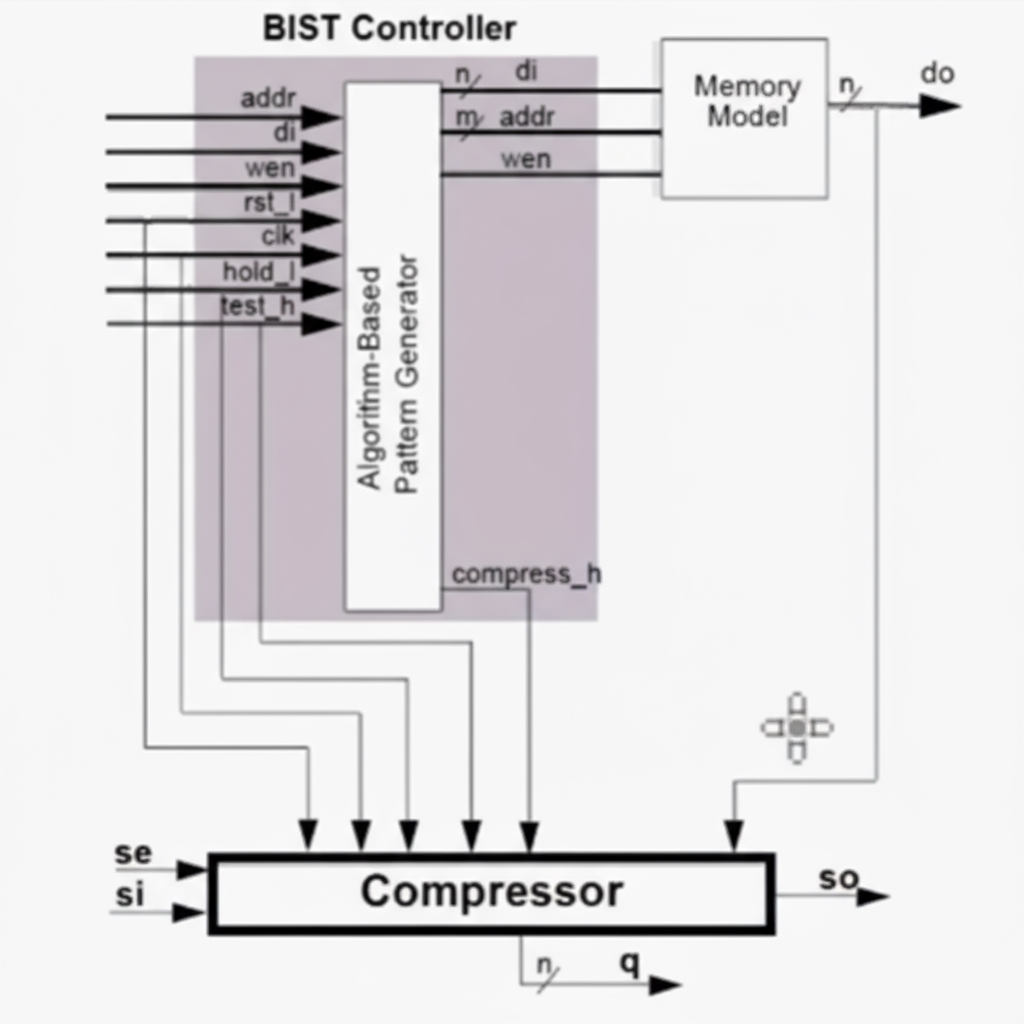

MBIST — Before or After Synthesis

14. Compressor for ROM

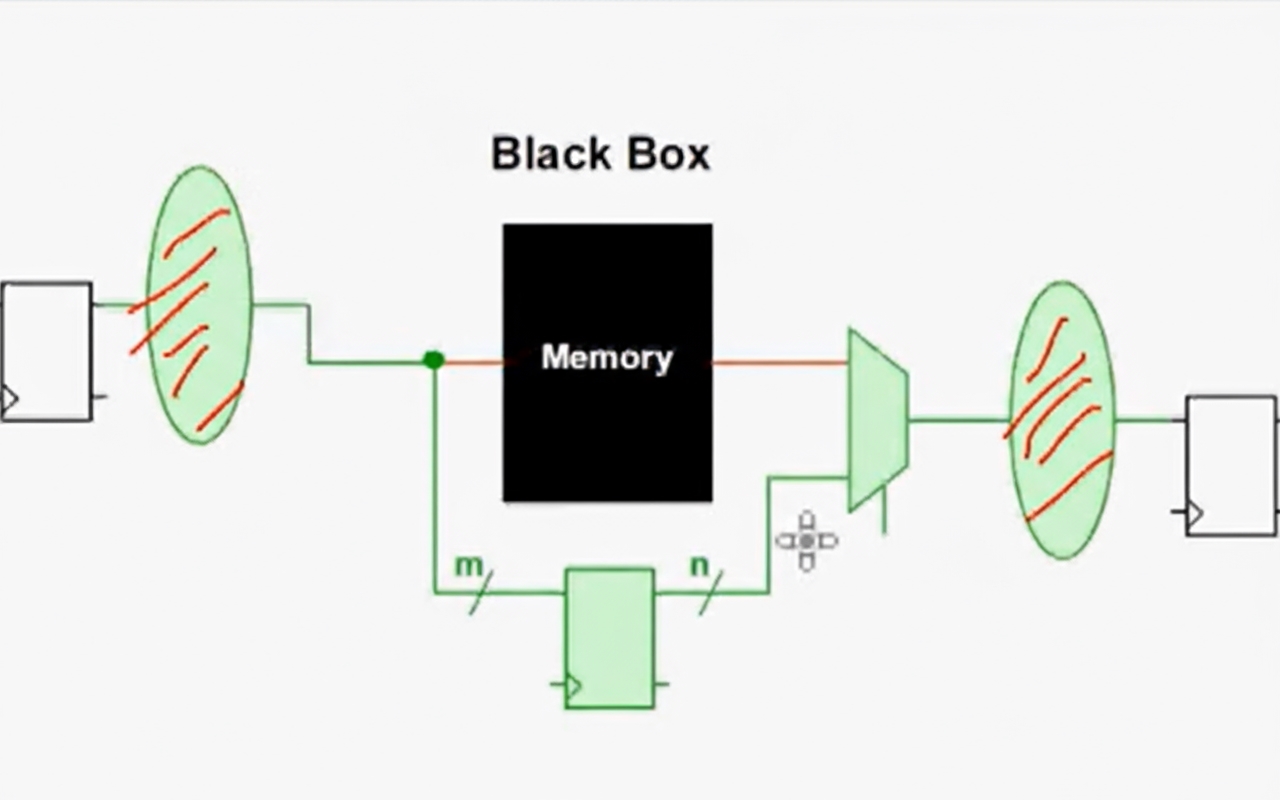

15. Dealing with Shadow Logic

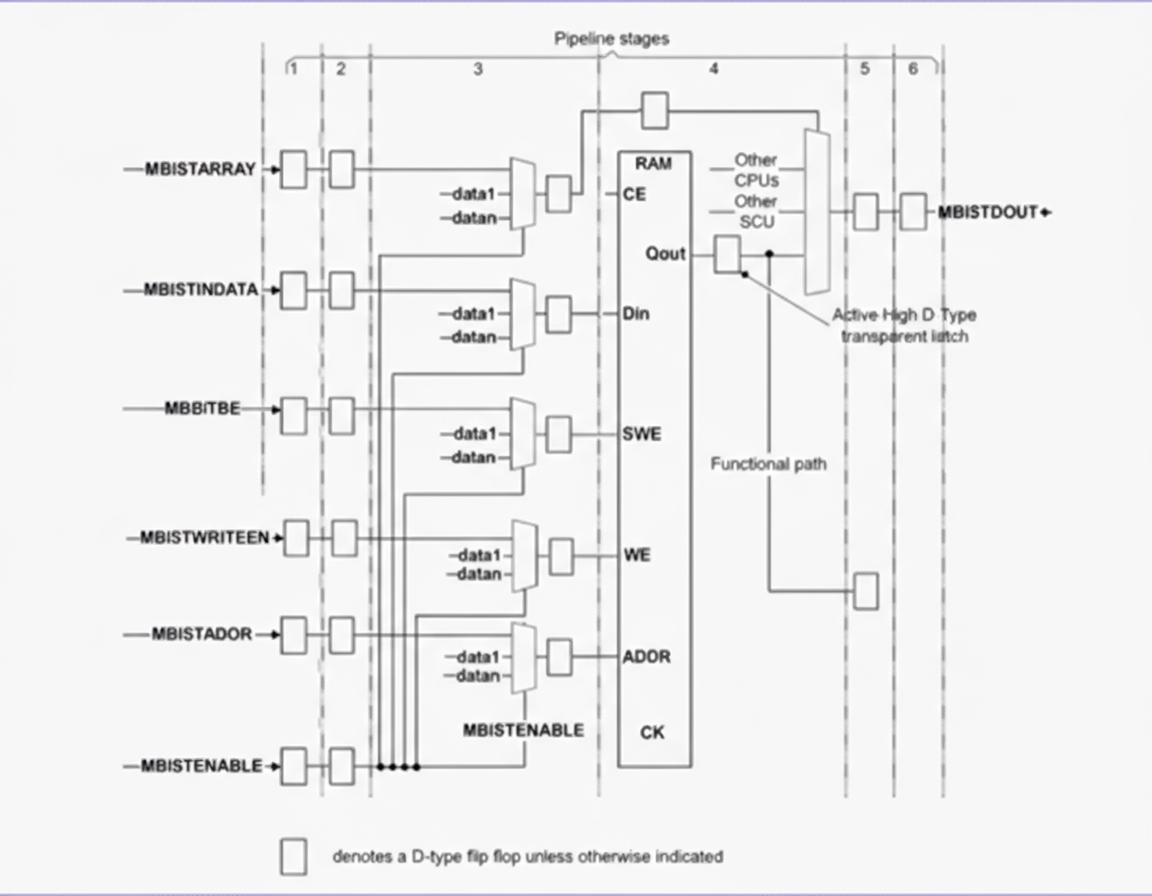

16. High-Speed Core MBIST

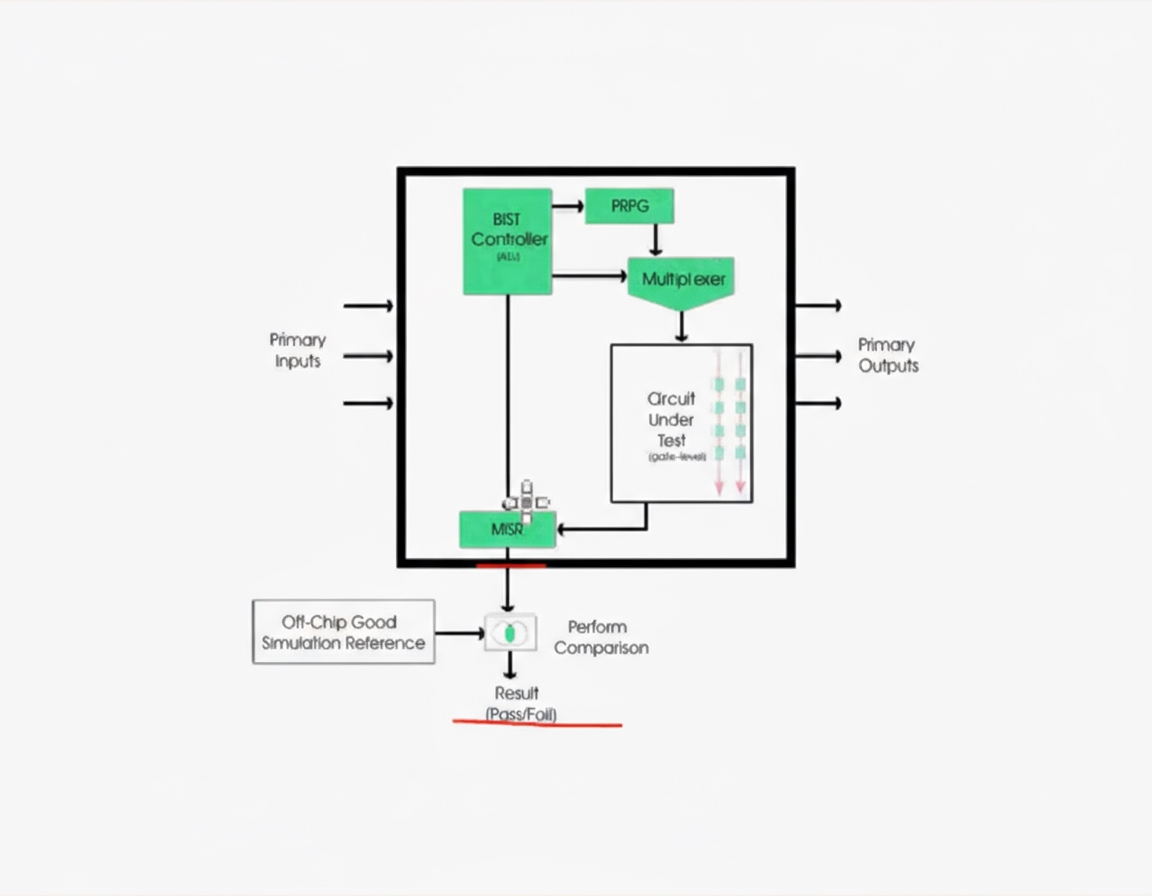

17. LBIST

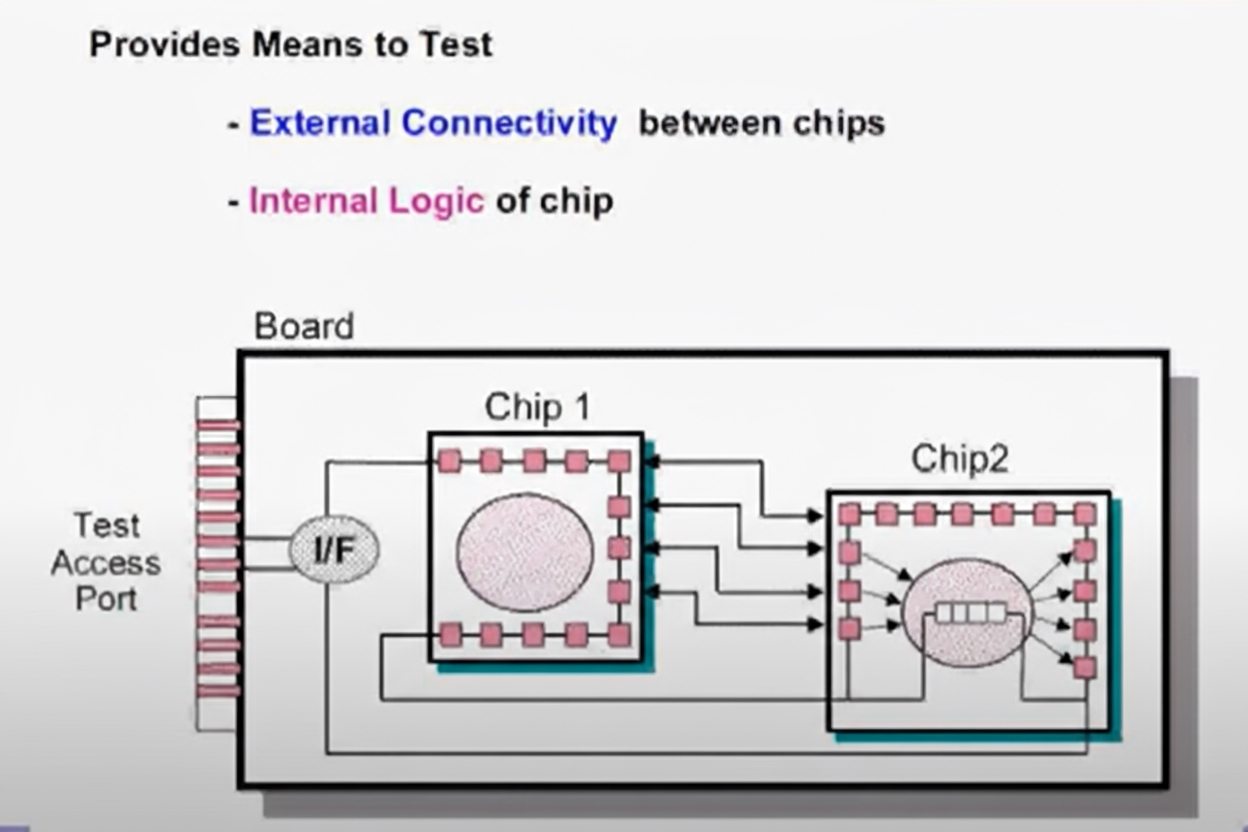

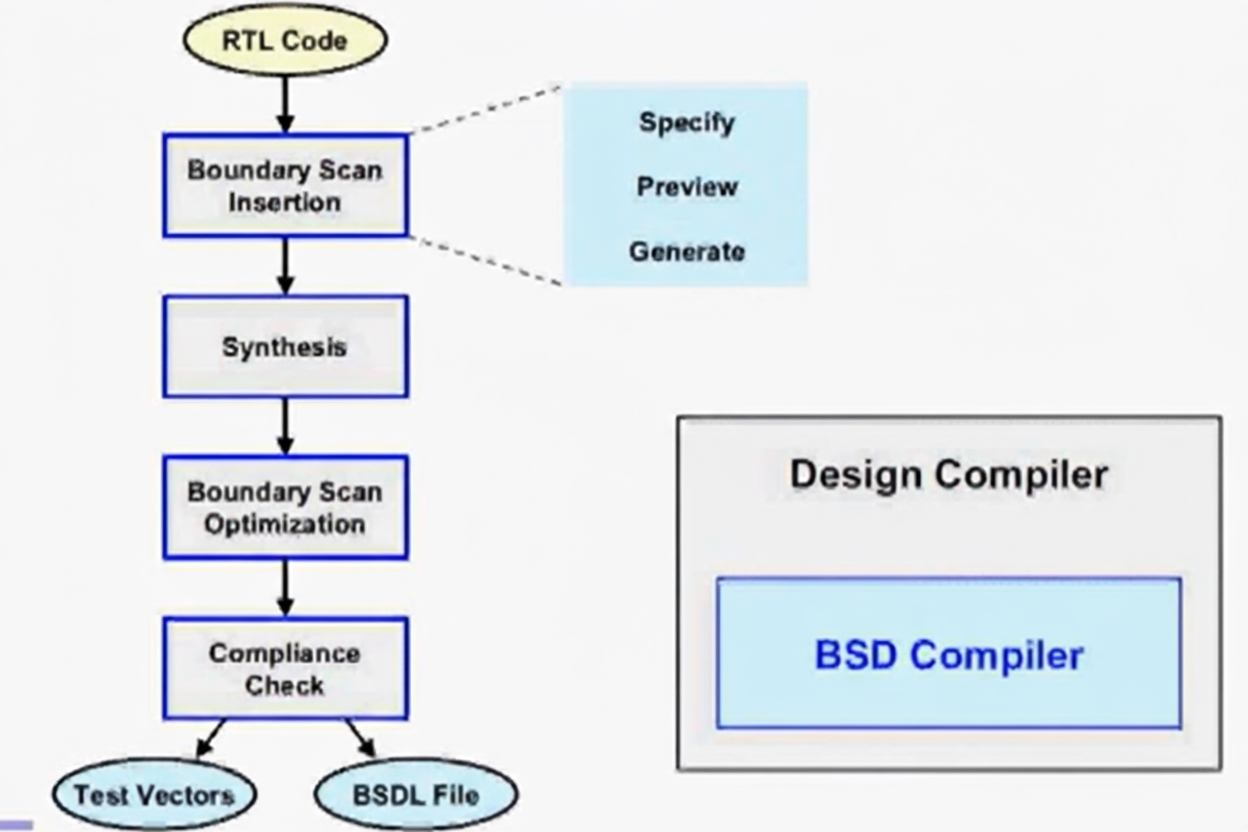

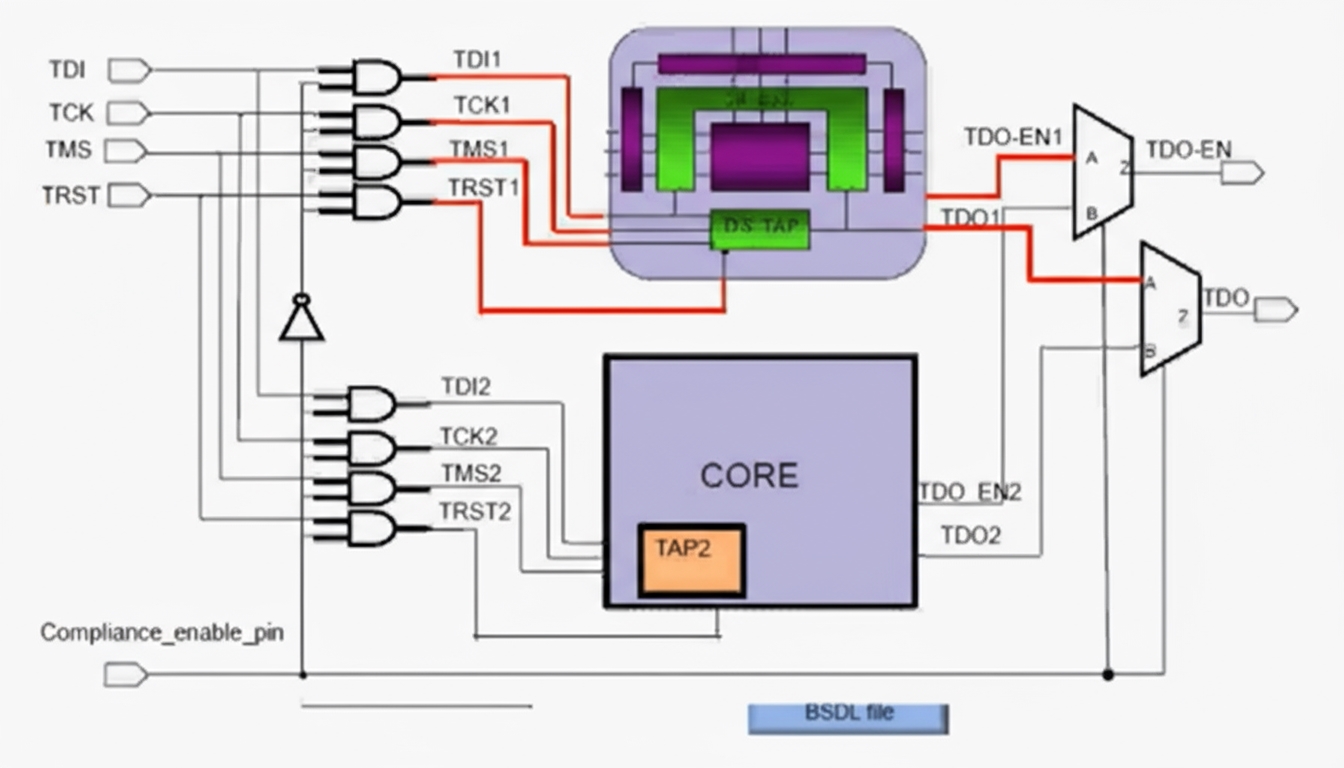

18. Boundary Scan

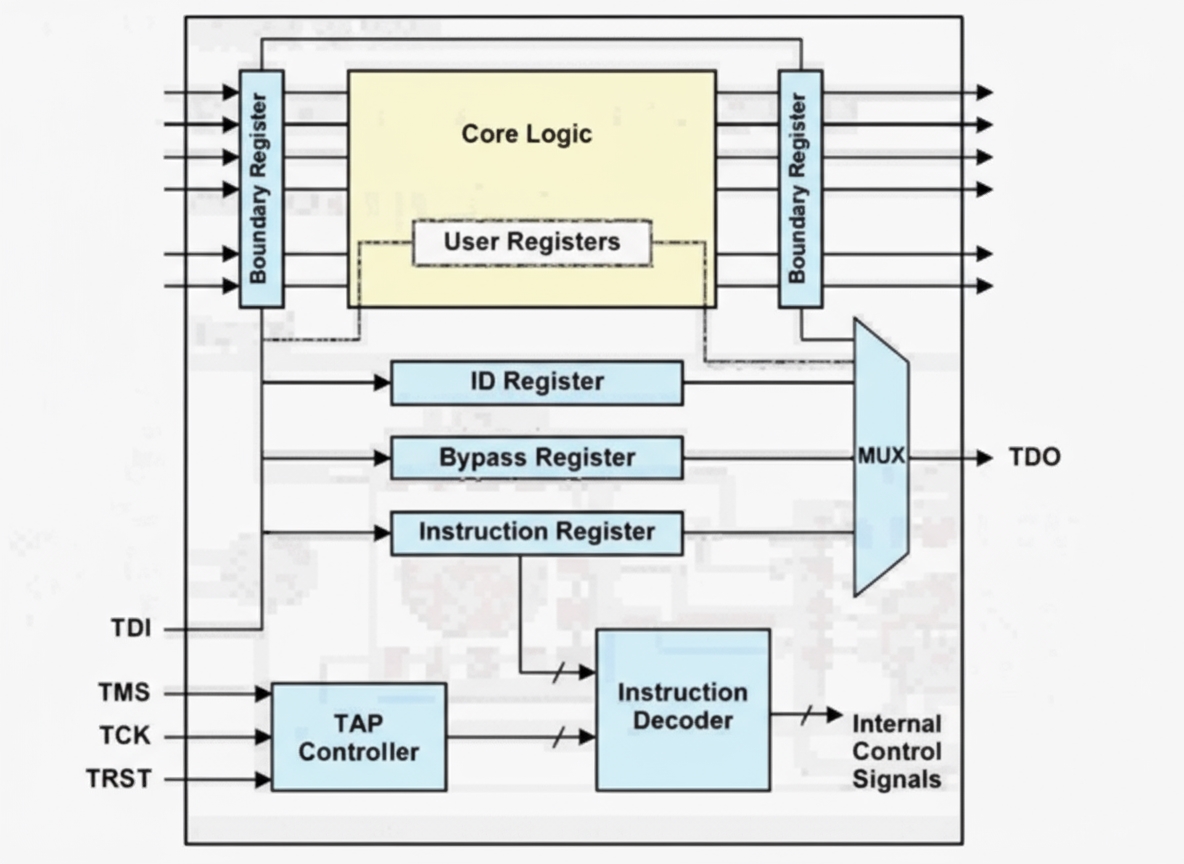

19. Boundary Scan Architecture

20. Process Defects — Physical Flaws

21. TAP Ports Hookup Pin (After Synthesis)

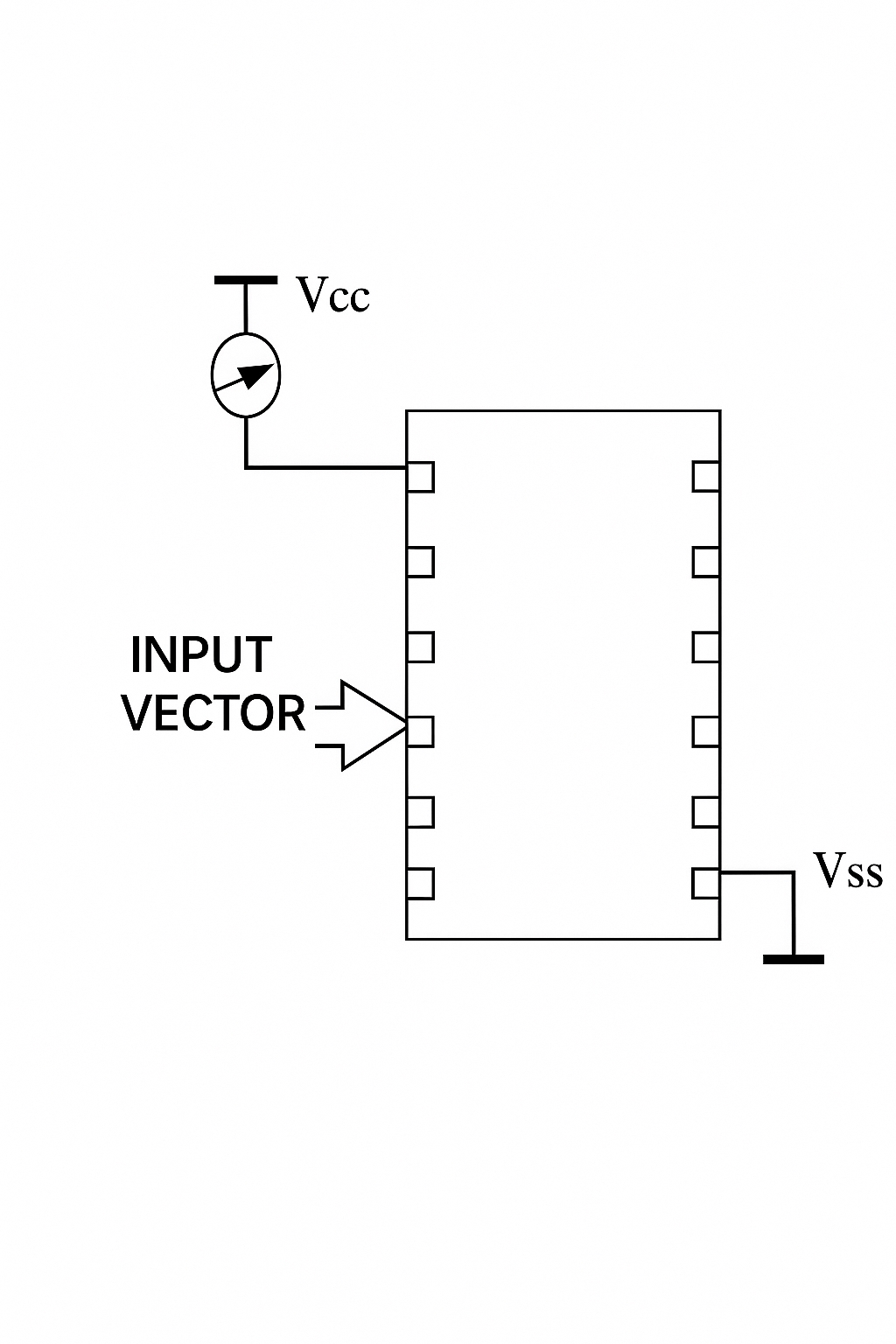

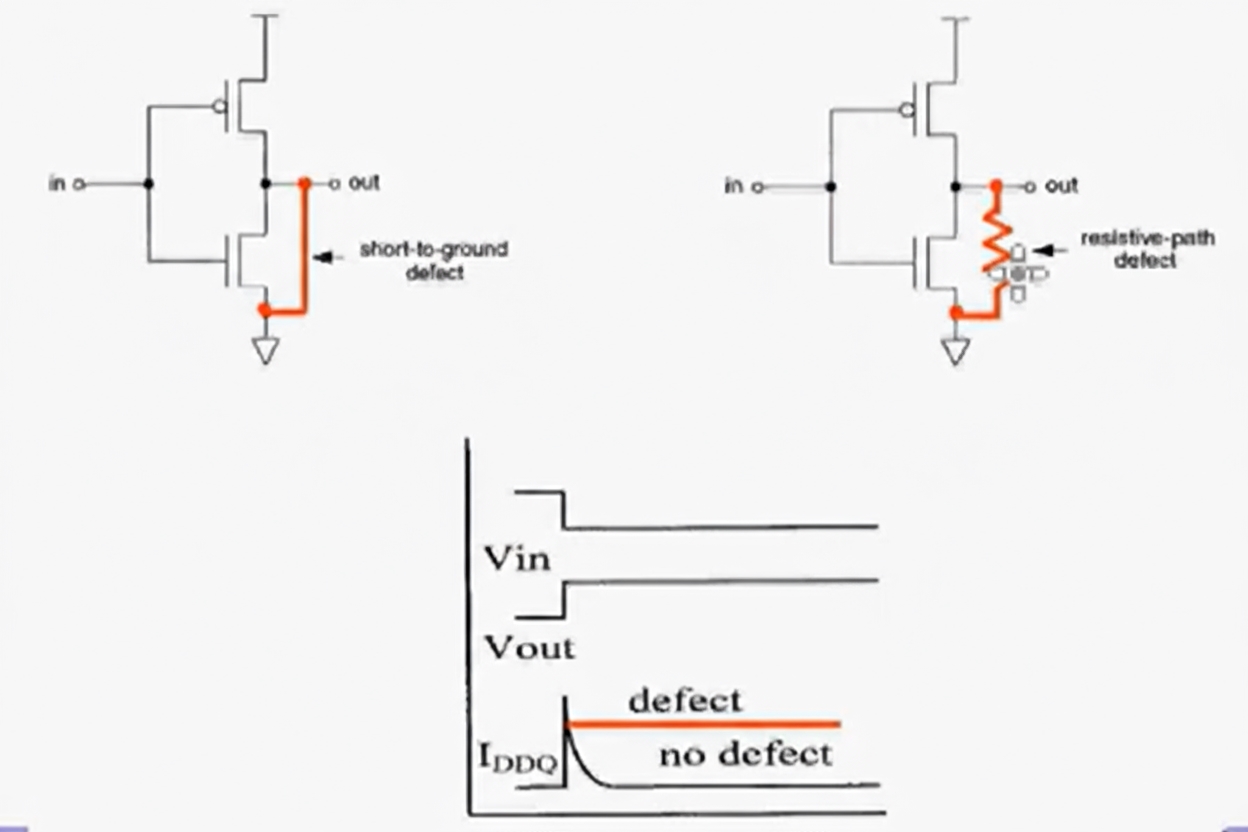

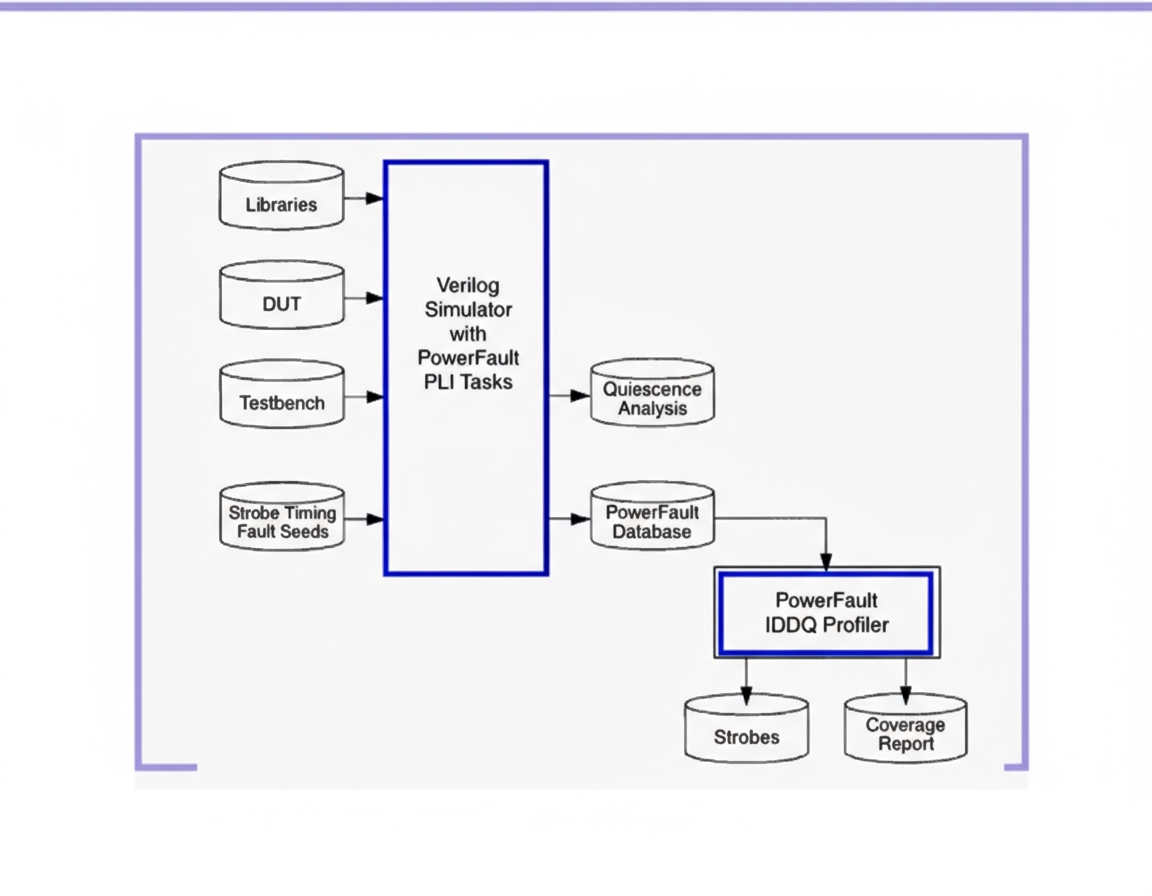

22. IDDQ

23. IDDQ Defects

24. Power Faults and IDDQ

Points to Consider Related to DFT

ALLPCB

ALLPCB