1. Overview

For years there has been a tug-of-war between FPGA and ASIC vendors over optimal solutions. New features introduced on FPGAs are often later hardened into ASICs to achieve lower cost, lower power, and greater capacity. In the early phase of a new product generation this iterative cycle tends to favor FPGA vendors, while long-term stable production tends to favor ASIC vendors.

In 2019, a new class of products began to change this dynamic. Xilinx introduced upgraded devices in the Zynq family with RF system-on-chip functionality that integrated ARM processor cores for some processing functions to reduce cost and power, programmable logic for beamforming, and on-chip ADC and DAC. The resulting power savings and reduced form factor are particularly attractive for large-scale MIMO radios.

2. Architectural trends: DFE and ADC/DAC integration

Integrating data conversion yields significant energy savings for remote radio units in 5G base stations. For every JESD204 channel the savings are on the order of 1 W, although per-antenna-stream savings vary. For a 64T massive MIMO configuration, more than 60 W can be saved from a 250 W thermal budget. While ASIC implementations can provide lower power for the integrated functions, the overall system-level savings are not always dramatic.

The important metric is total thermal dissipation rather than the benefit on an isolated optimized block. Constant-voltage thermal management in RRUs has delayed a straightforward migration to ASICs. Even tier-1 network equipment vendors currently partition the digital front end and data converters differently. There is not yet a single dominant implementation approach.

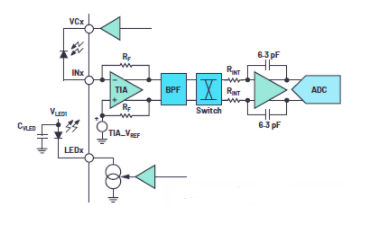

In Xilinx application examples, a key issue addressed was the power consumed by the JESD204 interface. Integrating the data converters with the digital front end greatly reduces the JESD204B overhead. Xilinx integrated DUC, DDC, and DPD with ADCs and DACs to eliminate the power overhead associated with the JESD204 link.

Another consideration for integrating processors and data converters is process node cadence. Processor logic on CMOS typically migrates down to the next process node (for example to 7 nm or 5 nm), while high-performance data converters are often developed on leading-edge nodes two to three generations ahead (approximately 18 nm for many converter designs).

3. Considerations when integrating RFSoC

Historically, once performance requirements are set, the market tends to scale to high volume and ASICs become attractive. For 5G there are still several immature variables. With REL-15 non-standalone deployments, the initial 5G rollout happened about a year earlier than some expected. While adoption is rapid and there is evidence that 5G is working, solutions released for commercial operation near the end of 2019 had limited time for optimization. Several aspects of 5G are still evolving:

- Beamforming: Implementations of beamforming continue to improve. Because beamforming algorithms often live in the RRU, a more flexible approach such as FPGA retains clear advantages.

- Channel bandwidth: Bandwidths are increasing. Early 5G systems commonly used 100 MHz per carrier, matching spectrum available to a single operator. There is a trend toward hardware that supports 200 MHz or more to reduce product variants and simplify manufacturing. Typical bands around 3.4–3.8 GHz meet most needs, but upcoming C-band auctions in the U.S. may allocate up to 280 MHz for 5G, increasing RRU performance demands.

- PA technology: Many mMIMO power amplifiers use GaN technology and benefit from flexible digital processing. Channel bandwidths rose from 100 MHz to 200 MHz and above, and power levels as well as digital predistortion require further optimization. PA development cycles can be shorter than those of large silicon projects, so locking in digital-processing features too early can restrict leveraging upcoming GaN performance improvements.

- O-RAN: Open RAN is an emerging standard that is gaining traction, but implementation details are still fluid. Split definitions such as option 7.2x are being finalized while operators are evaluating alternative splits that move key functions in or out of the RRU, such as precoding, layer mapping, and channel estimation. Where computation occurs affects processor requirements and will take years to settle.

These uncertainties extend the useful life of more flexible designs. With long-term 5G benefits still somewhat unclear, flexibility is critical to accommodate evolving system requirements.

4. FPGA, ASIC and RFSoC

The main drivers for RFSoC integration discussed above are reduced power, cost, and board area.

The top three OEMs historically used ASICs for production of FDD and TDD LTE base stations. They had sufficient volume to justify ASIC development, and LTE deployments were stable enough to consolidate customers on a common ASIC platform. With 5G complexity, the economics of ASICs push the required annual volume threshold much higher, to roughly 200,000 units per year, to justify the cost of developing an ASIC for all major network OEMs.

Market volumes for 5G are currently uneven. For 2020, analysts forecast roughly 115 million 5G transceivers shipped (each transceiver is a unique transmit path). Assuming each RFSoC or ASIC supports about eight transmit chains, the number of ASICs/FPGAs would be about 14 million, with roughly 80 percent consumed in China. For vendors closely tied to major Chinese OEMs, there are clear reasons to move to ASIC solutions based on supply choices. For vendors with primary markets outside China, the decision is less clear. In 2020, outside China, Asia/FPGAs slots were roughly 250-3M, with differences across many countries and operators. Most 5G deployments range from 100 to 10,000 base stations, so any single operator deployment is usually not enough to justify ASIC use. Only the combined volumes of major OEMs would justify investment in ASICs. As the market assesses real-world 5G performance and moves toward 5G standalone deployments, the need for flexible system design remains.

New 5G use cases require greater RAN flexibility. Initial 5G rollouts focused on mobile users and enhanced mobile broadband (eMBB) for smartphones. Unlike 4G, 5G introduces two additional service types: IoT and URLLC (ultra-reliable low-latency communications). Over the long term, these are expected to generate substantial B2B revenue, but that outcome depends on the deployed 5G infrastructure and subsequent evolution. RRUs must support deployments inside buildings or as private leased networks connected via C-RAN architectures. The data requirements for these use cases are not yet fully clear and may differ from current eMBB approaches. Flexibility in data handling will be important to support and introduce these new applications smoothly.

5G brings additional system complexity. Each telecom generation improves user experience through better voice or more data; 5G continues this trend. The networks being deployed today are infrastructure that will be augmented and expanded. The 5G ecosystem includes macro sites, indoor RRUs, repeaters, and small cells, each with different requirements. Processors that support this diversity must be flexible and able to adapt to evolving use cases that are not fully understood before large-scale deployment.

There is no doubt that 5G will drive unprecedented data consumption for consumers and enterprises, with increased architectural complexity. Massive MIMO significantly improves performance and creates large data volumes. Data processing is a core architectural consideration for network equipment vendors. The typical migration from programmable solutions to hardened implementations may not be optimal when 5G is still new and its performance at scale is not fully characterized. Given the new normal in network traffic, the ability to rapidly adapt key hardware components will be critical in the coming years.

ALLPCB

ALLPCB