Key questions for IC design

Which IP and EDA tools are required to support 3DIC and Chiplet die-to-die interconnects and heterogeneous integration? As IoT edge computing gains importance, what kinds of processors are needed at the edge? Under current geopolitical pressures, how can the RISC-V open architecture ecosystem continue to evolve? With advances in artificial intelligence and machine learning, how can China’s EDA and IP companies accelerate integration into the integrated circuit industry and value chains?

Trends driving higher requirements

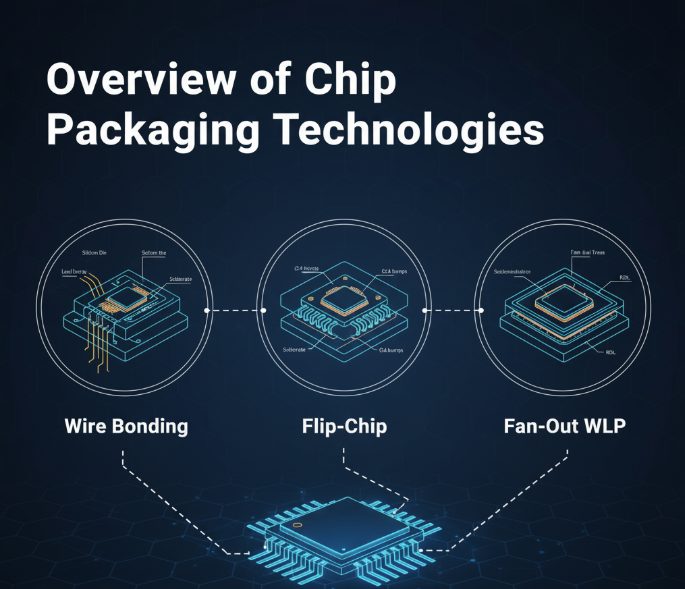

With an overall recovery in the global integrated circuit industry, the IC design market has been growing rapidly. Advanced process nodes continue to evolve while transistor dimensions approach physical limits. At the same time, large language models such as ChatGPT are driving up compute requirements for chips, pushing AI chip designs toward Chiplet-based packaging and other advanced approaches to achieve better power, performance, and area (PPA) beyond traditional Moore-scaling.

Implications for EDA and IP

In the post-Moore era, upstream IC design tools and IP face heightened demands. Supporting 3DIC and Chiplet die-to-die interconnects, as well as heterogeneous integration, requires new classes of IP and EDA tool capabilities. Edge computing trends also affect processor design choices and system partitioning. Meanwhile, the evolution of the RISC-V ecosystem needs sustained technical and ecosystem efforts to remain viable under changing geopolitical conditions.

Industry forum

At the IIC Shenzhen 2023 exhibition and conference, ASPENCORE organized a concurrent "EDA/IP and IC Design Forum" where representatives from companies such as Cadence, Arm, Imagination, Xinhe Semiconductor, Kuixin Technology, Canxin Semiconductor, and Xinlai Technology discussed these challenges and potential technical and ecosystem responses.

ALLPCB

ALLPCB