In the fast-paced world of mobile phone technology, designing a reliable Power Distribution Network (PDN) for printed circuit boards (PCBs) is crucial. A well-designed PDN ensures stable power delivery, minimizes noise, and prevents performance issues in compact, high-speed devices. If you're wondering how to optimize PCB PDN design, this guide will walk you through the essentials, from decoupling capacitors to power plane impedance, voltage drop analysis, and PDN simulation. We'll break down complex concepts into simple, actionable insights to help engineers and designers achieve efficient power delivery in mobile phone PCBs.

What Is a Power Distribution Network (PDN) in Mobile Phone PCBs?

A Power Distribution Network, or PDN, is the system within a PCB that delivers power from the source (like a battery or voltage regulator) to all the components on the board. In mobile phones, where space is tight and power demands are high, the PDN must provide stable voltage levels while managing noise and minimizing losses. A poorly designed PDN can lead to voltage drops, signal interference, and even device failure.

The goal of PDN design is to maintain power integrity, ensuring that every chip, sensor, and module in a mobile phone gets the clean, consistent power it needs. This involves careful planning of power planes, ground planes, and components like decoupling capacitors. Let's dive into the key aspects of PCB PDN design for mobile phones.

Key Challenges in Mobile Phone PCB PDN Design

Mobile phones are packed with high-speed processors, multiple sensors, and wireless modules, all squeezed into a tiny form factor. This creates unique challenges for PDN design, including:

- High Current Demands: Modern mobile phone processors can draw currents exceeding 5A during peak operation, requiring a PDN that can handle sudden spikes without voltage drops.

- Limited Space: With PCBs measuring just a few square inches, there’s little room for extensive power planes or large capacitors.

- Noise Sensitivity: High-frequency components like 5G modems and CPUs are sensitive to power supply noise, which can degrade signal integrity.

- Thermal Constraints: Power losses in the PDN generate heat, which is hard to dissipate in a compact device.

Addressing these challenges requires a deep understanding of PDN components and design strategies. Let's explore the critical elements that ensure stable power delivery.

Core Elements of PCB PDN Design

1. Power Planes and Ground Planes

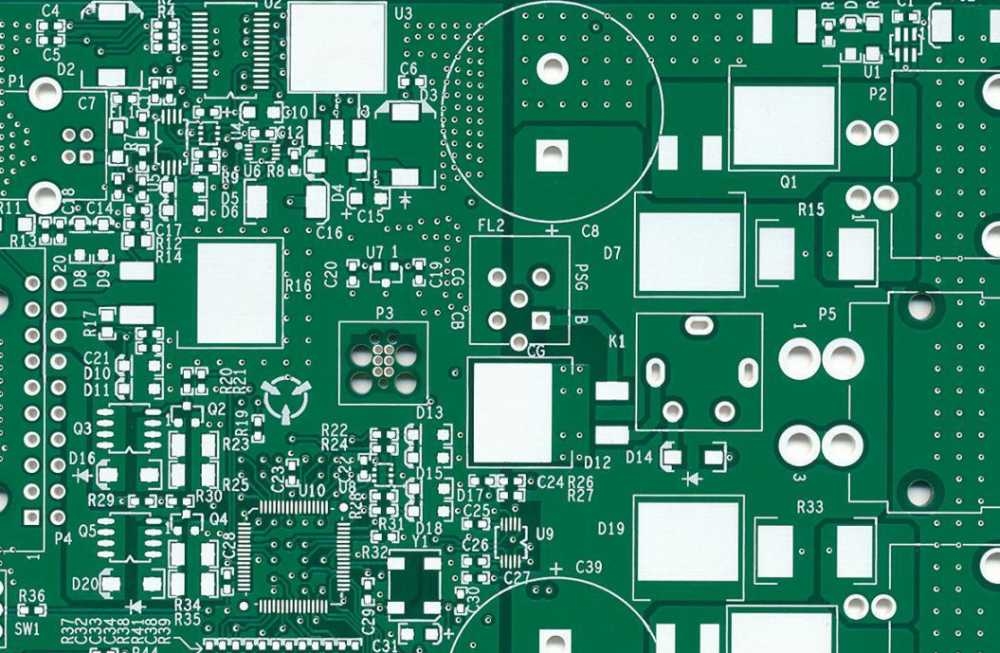

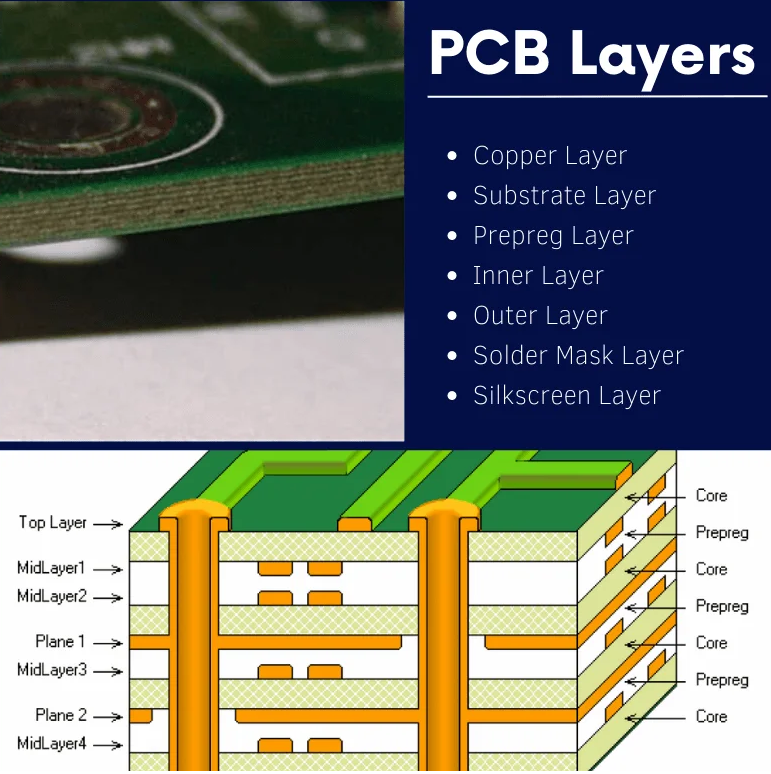

Power planes and ground planes are large, continuous layers of copper in a PCB that distribute voltage and provide a return path for current. In mobile phone PCBs, these planes are essential for reducing impedance and ensuring uniform power delivery. A typical mobile phone PCB might have a 3.3V power plane for sensors and a 1.8V plane for digital circuits, each paired with a ground plane to minimize noise.

The impedance of these planes, often measured in milliohms, must be kept as low as possible. For instance, a power plane with an impedance of 10 mΩ or less can significantly reduce voltage drops during high-current events. Designers achieve this by using thicker copper layers (e.g., 1 oz or 2 oz per square foot) and minimizing the distance between power and ground planes.

2. Decoupling Capacitors in PDN Design

Decoupling capacitors are small components placed near power pins of ICs to filter out noise and provide instantaneous current during sudden demand spikes. In mobile phone PCBs, where switching frequencies can reach several GHz, decoupling capacitors are critical for maintaining power integrity.

For example, a typical mobile phone processor might require multiple capacitors with values ranging from 0.1 μF to 10 μF, placed within 1-2 mm of the power pins. These capacitors reduce high-frequency noise by acting as local energy reservoirs. However, improper placement or selection can lead to resonance issues, where the PDN impedance peaks at certain frequencies, amplifying noise.

Best practices for using decoupling capacitors include:

- Choosing capacitors with low equivalent series resistance (ESR) and inductance (ESL), often below 100 mΩ and 1 nH, respectively.

- Placing smaller capacitors closer to the IC for high-frequency noise suppression, and larger ones further away for bulk energy storage.

- Using multiple capacitor values to cover a wide frequency range, avoiding resonance peaks.

3. Power Plane Impedance and Its Impact

Power plane impedance refers to the opposition a power plane offers to the flow of alternating current (AC). High impedance can cause voltage fluctuations, especially at high frequencies common in mobile phone circuits (e.g., 100 MHz to 1 GHz). Keeping impedance low is vital for stable power delivery.

Impedance is influenced by the plane’s geometry, material properties, and the presence of vias or cuts in the plane. For instance, a power plane split by a via or trace can increase impedance by 20-30%, leading to uneven power distribution. Designers often use simulation tools to model power plane impedance and identify problem areas before manufacturing.

A target impedance of less than 1 mΩ at critical frequencies is often ideal for mobile phone PDNs. Achieving this might involve stacking power and ground planes closely (e.g., separated by 5-10 mils of dielectric) to enhance capacitance and reduce impedance.

Voltage Drop Analysis in Mobile Phone PDNs

Voltage drop occurs when the voltage at a component’s power pin is lower than the source voltage due to resistance and inductance in the PDN. In mobile phones, even a small drop of 50 mV can affect performance, especially for low-voltage components operating at 1.2V or below.

To analyze voltage drops, engineers calculate the DC resistance of power traces and planes using Ohm’s Law (V = I × R). For example, a power trace carrying 2A with a resistance of 10 mΩ will cause a voltage drop of 20 mV. This analysis helps determine if wider traces or additional vias are needed to reduce resistance.

Dynamic voltage drops, caused by sudden current demands, are also critical. These are often evaluated using PDN simulation tools that model transient behavior. If a processor switches from idle to full load in 1 μs, the PDN must supply the surge without dropping below the minimum voltage threshold (e.g., 95% of nominal voltage).

PDN Simulation: A Must for Modern Mobile Phone Designs

PDN simulation is a powerful tool for predicting and optimizing power integrity in mobile phone PCBs. These simulations analyze impedance profiles, voltage drops, and noise levels before the board is built, saving time and cost.

Common simulation approaches include:

- Frequency Domain Analysis: Measures power plane impedance across a range of frequencies (e.g., 1 kHz to 1 GHz) to identify resonance peaks. A peak impedance above 10 mΩ at critical frequencies might indicate a need for additional decoupling capacitors.

- Time Domain Analysis: Simulates transient events, like a processor waking from sleep mode, to ensure voltage stability during current spikes.

- Thermal Analysis: Evaluates heat generation due to power losses in the PDN, critical for compact mobile phone designs where temperatures can exceed 60°C.

Simulation tools allow designers to test different layouts, capacitor placements, and plane configurations virtually. For instance, adjusting the spacing between power and ground planes from 10 mils to 5 mils might reduce impedance by 40%, a change that can be validated through simulation before production.

Best Practices for Optimizing PCB PDN Design in Mobile Phones

Here are some practical tips to ensure a robust PDN for mobile phone PCBs:

- Minimize Plane Splits: Avoid cutting power or ground planes unnecessarily, as splits increase impedance and create noise paths.

- Use Multiple Vias: Connect power planes to IC pins with multiple vias to reduce resistance and inductance. For high-current pins, 3-5 vias per connection are often recommended.

- Optimize Capacitor Placement: Place decoupling capacitors as close as possible to power pins, ideally within 1 mm, to minimize loop inductance.

- Balance Power and Ground Layers: In a 6-layer PCB, allocate at least one dedicated power plane and one ground plane, positioned adjacent to each other for low impedance.

- Simulate Early and Often: Run PDN simulations at multiple design stages to catch issues before they become costly manufacturing errors.

Why PDN Design Matters for Mobile Phone Performance

A well-designed PDN directly impacts the reliability and performance of a mobile phone. Stable power delivery ensures that high-speed processors run without glitches, wireless modules maintain signal strength, and battery life is maximized by reducing power losses. Conversely, a flawed PDN can cause random reboots, dropped calls, or sluggish performance—issues no user wants to experience.

For engineers, mastering PCB PDN design means balancing multiple factors: space constraints, cost, and performance requirements. By focusing on low power plane impedance, strategic use of decoupling capacitors, thorough voltage drop analysis, and leveraging PDN simulation, you can create mobile phone PCBs that meet the demands of modern technology.

Conclusion

Designing a Power Distribution Network for mobile phone PCBs is both a science and an art. It requires careful attention to power plane impedance, strategic placement of decoupling capacitors, precise voltage drop analysis, and the use of PDN simulation to predict and solve issues. As mobile devices continue to push the boundaries of speed and efficiency, a robust PDN becomes more important than ever.

By following the principles and best practices outlined in this guide, engineers can ensure stable power delivery in even the most compact and demanding mobile phone designs. Whether you're working on a flagship smartphone or a budget device, optimizing your PCB PDN design is the key to delivering reliable, high-performance products.

ALLPCB

ALLPCB