When designing a printed circuit board (PCB), one critical factor that often gets overlooked is via-to-via spacing, especially when dealing with different electrical potentials. So, how does via-to-via spacing work in different potential scenarios? Simply put, via-to-via spacing must be carefully calculated to prevent electrical interference, arcing, or breakdown between vias carrying different voltages. The spacing depends on factors like the voltage difference, dielectric material, environmental conditions, and industry standards.

In this blog, we’ll dive deep into the concept of via-to-via spacing in different potential designs. We’ll explore why it matters, the factors influencing spacing requirements, and practical guidelines to ensure your PCB performs reliably. Whether you’re a beginner or a seasoned engineer, this guide will provide valuable insights to optimize your designs for safety and efficiency.

What Is Via-to-Via Spacing and Why Does It Matter?

Vias are small holes in a PCB that allow electrical connections between different layers. When two vias carry different electrical potentials (voltages), the spacing between them becomes crucial. If the vias are too close, there’s a risk of electrical arcing, short circuits, or dielectric breakdown, which can damage the board or cause system failure.

Via-to-via spacing refers to the physical distance between the centers or edges of two adjacent vias. This spacing is especially important in high-voltage or mixed-signal designs where different potentials are present. Proper spacing ensures:

- Safety by preventing arcing or shorts.

- Reliability by reducing interference between signals.

- Compliance with industry standards like IPC (Institute of Printed Circuits) guidelines.

For instance, in a design with a 5V signal via next to a 50V power via, insufficient spacing could lead to crosstalk or even a catastrophic failure if the voltage difference causes a spark. That’s why understanding and applying correct spacing rules is essential for every PCB designer.

Factors Influencing Via-to-Via Spacing in Different Potentials

Several factors determine the minimum via-to-via spacing in designs with different potentials. Let’s break them down to understand how each impacts your PCB layout.

1. Voltage Difference Between Vias

The greater the voltage difference between two vias, the larger the spacing required. This is because higher voltage differences increase the risk of electrical arcing or breakdown through the air or dielectric material. For example:

- For a 50V difference, spacing might need to be at least 0.6mm (24 mils) under certain conditions.

- For a 500V difference, spacing could increase to 3mm (118 mils) or more, depending on the dielectric strength and environment.

These values are general estimates and should be verified against specific standards or design requirements, but they highlight how voltage directly affects spacing needs.

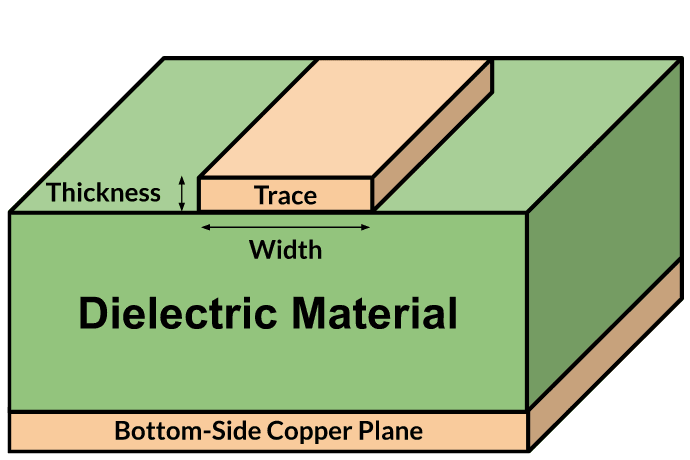

2. Dielectric Material and Board Thickness

The material used in your PCB, such as FR-4, and the thickness of the board play a significant role in determining safe spacing. Dielectric materials have a specific breakdown voltage, which is the point at which they fail to insulate. FR-4, a common PCB material, has a dielectric strength of about 20 kV/mm. Thicker boards or materials with higher dielectric strength allow for closer via spacing, while thinner boards may require more distance.

3. Environmental Conditions

Environmental factors like humidity, temperature, and altitude can impact via spacing requirements. High humidity or low air pressure (at high altitudes) reduces the insulating properties of air, increasing the risk of arcing. For designs used in harsh environments, you might need to increase spacing beyond standard recommendations or apply conformal coating for added protection.

4. Industry Standards and Regulations

PCB designs must comply with standards like IPC-2221, which provides guidelines for spacing based on voltage levels and application types. These standards categorize designs into different classes (e.g., consumer electronics, industrial, or medical) and provide specific spacing rules for internal and external layers. Adhering to these rules ensures your design is safe and manufacturable.

Calculating Via-to-Via Spacing for Different Potentials

To calculate the correct via-to-via spacing, you need to consider both creepage and clearance distances. These terms are often used interchangeably, but they have distinct meanings in PCB design.

Creepage vs. Clearance

Creepage is the shortest path between two conductive parts along the surface of the insulating material. Clearance is the shortest distance through the air between two conductive parts. Both must be considered when determining via spacing, especially in high-voltage designs.

- Clearance prevents arcing through the air. For a 100V difference, a clearance of 0.8mm (31 mils) might be required.

- Creepage prevents surface breakdown due to contamination or moisture. For the same 100V, creepage might need to be 1.2mm (47 mils) on an uncoated board.

Using IPC Guidelines for Spacing

The IPC-2221 standard provides detailed tables for minimum spacing based on voltage and application. For example:

- For internal layers (not exposed to air), spacing can be smaller because there’s no risk of arcing through air.

- For external layers, spacing must account for environmental factors, often requiring 2-3 times the internal spacing.

As a rule of thumb, for voltages below 100V, a via-to-via spacing of 0.5mm (20 mils) is often sufficient for internal layers. For higher voltages, refer to specific tables in the IPC standards or use design software that incorporates these rules.

Practical Tips for Via Spacing in Different Potential Designs

Now that we’ve covered the theory, let’s look at some actionable tips to apply proper via-to-via spacing in your PCB designs with different potentials.

1. Use Design Software With Built-In Rules

Modern PCB design tools allow you to set design rules for via spacing based on voltage levels. These tools can automatically flag violations, saving time and reducing errors. Make sure to input the correct voltage ratings for nets to enforce appropriate spacing.

2. Separate High and Low Voltage Areas

Whenever possible, physically separate high-voltage and low-voltage sections on your PCB. This reduces the risk of interference and allows for tighter spacing within each section. For example, place power vias on one side of the board and signal vias on the other, using ground planes as barriers.

3. Add Insulation or Coating for High-Voltage Designs

For high-voltage applications (above 300V), consider adding a conformal coating or using a higher-grade dielectric material. This can reduce the required spacing by improving insulation, though it may increase manufacturing costs.

4. Minimize Via Density in High-Voltage Areas

In areas with significant voltage differences, avoid placing vias too densely. Increased density raises the risk of breakdown, especially if manufacturing tolerances lead to slight misalignments. A good practice is to maintain at least 2-3 times the minimum spacing in critical areas.

Common Mistakes to Avoid With Via-to-Via Spacing

Even experienced designers can make mistakes when it comes to via spacing. Here are some common pitfalls and how to avoid them.

1. Ignoring Environmental Factors

Failing to account for humidity or temperature can lead to insufficient spacing. Always design with the worst-case scenario in mind, especially for industrial or outdoor applications.

2. Overlooking Internal Layer Spacing

While internal layers have lower spacing requirements, they’re not immune to breakdown. Ensure that even internal vias meet minimum spacing rules, especially in multilayer boards with high-voltage signals.

3. Not Consulting Manufacturing Capabilities

Every manufacturer has specific capabilities and tolerances for via drilling and spacing. Before finalizing your design, check with your fabrication partner to ensure your spacing is achievable. For example, some manufacturers may struggle with vias closer than 0.3mm (12 mils) center-to-center due to drilling precision.

Via Spacing in Mixed-Signal and High-Speed Designs

In mixed-signal or high-speed PCB designs, via-to-via spacing takes on additional importance beyond just voltage differences. Here, spacing also affects signal integrity and electromagnetic interference (EMI).

For high-speed signals, vias should be spaced to minimize crosstalk. A common guideline is the 3W rule, where the center-to-center spacing between traces (or vias) should be at least three times the width of the trace. While this primarily applies to traces, it can be adapted for vias in high-speed designs to reduce interference.

In mixed-signal designs, spacing between analog and digital vias prevents noise coupling. For instance, placing analog signal vias too close to digital clock vias (even at similar potentials) can introduce noise, degrading performance. A spacing of 1mm (40 mils) or more, combined with ground plane separation, often helps mitigate these issues.

Conclusion: Mastering Via-to-Via Spacing for Reliable PCB Designs

Via-to-via spacing in different potential scenarios is a fundamental aspect of PCB design that directly impacts safety, reliability, and performance. By understanding the factors that influence spacing—such as voltage differences, dielectric materials, and environmental conditions—you can create designs that meet industry standards and perform flawlessly in real-world applications.

Start by calculating creepage and clearance distances using guidelines like IPC-2221. Leverage design tools to enforce spacing rules, separate high and low-voltage areas, and always consider manufacturing capabilities. Whether you’re working on a simple consumer device or a complex high-voltage system, proper via spacing ensures your PCB stands the test of time.

With these insights and tips, you’re well-equipped to tackle via-to-via spacing challenges in your next project. Focus on precision, adhere to best practices, and your designs will achieve both functionality and durability.

ALLPCB

ALLPCB