In the world of electronics design, ensuring the reliability of printed circuit boards (PCBs) is critical. One major challenge designers face is minimizing electromagnetic interference (EMI) caused by electrostatic discharge (ESD) events. So, how can you design a PCB layout to reduce EMI from ESD? The answer lies in strategic layout techniques such as proper grounding, optimized trace routing, and transient suppression methods. In this comprehensive guide, we'll dive deep into effective PCB layout strategies for EMI reduction and ESD protection, providing actionable tips to help engineers create robust and reliable designs.

Understanding EMI and ESD in PCB Design

Before exploring specific techniques, let’s clarify what EMI and ESD mean in the context of PCB design. Electromagnetic interference (EMI) refers to unwanted electrical noise that disrupts the performance of electronic devices. This noise can come from external sources or internal components, often leading to signal distortion or system failures. Electrostatic discharge (ESD), on the other hand, is a sudden flow of electricity between two objects caused by a buildup of static charge. ESD events can generate high-voltage spikes—sometimes exceeding 15,000 volts in extreme cases—that induce EMI, potentially damaging sensitive components or causing malfunctions.

In PCB design, ESD events are a common source of EMI because they create rapid voltage transients that radiate electromagnetic fields or couple into nearby traces. Reducing EMI from ESD events requires a proactive approach during the layout phase, focusing on grounding, routing, and suppression techniques. Let’s explore these strategies in detail to help you build more resilient designs.

Key PCB Layout Techniques for EMI Reduction and ESD Protection

Creating a PCB layout that minimizes EMI from ESD events involves several best practices. Below, we’ll break down the most effective techniques, focusing on grounding, trace routing, and transient suppression, to ensure your design remains robust under challenging conditions.

1. Implement Solid Grounding Practices

Grounding is the foundation of any EMI reduction strategy. A well-designed ground plane acts as a low-impedance path for return currents, preventing the buildup of noise that can amplify EMI during ESD events. Here are some key grounding tips:

- Use a Continuous Ground Plane: Place a solid ground plane on one layer of your PCB, ideally directly below the signal layer. This minimizes loop areas where EMI can couple into traces. For two-layer boards, if a full ground plane isn’t possible, use a gridded ground structure to emulate a plane, connecting ground traces in a network to cover as much area as possible.

- Minimize Ground Loops: Large ground loops act as antennas, picking up or radiating EMI. Keep return paths short and direct by placing ground vias near signal vias, ensuring currents flow through the shortest possible path.

- Separate Analog and Digital Grounds: If your design includes both analog and digital circuits, split the ground plane into distinct sections to prevent digital noise from interfering with sensitive analog signals. Connect these planes at a single point near the power supply to avoid ground loops.

By prioritizing grounding, you create a stable reference for signals, reducing the risk of EMI during high-voltage ESD strikes. For example, a continuous ground plane can reduce noise coupling by up to 20 dB compared to poorly grounded designs.

2. Optimize Trace Routing for EMI Control

Trace routing plays a crucial role in minimizing EMI from ESD events. Poorly routed traces can act as antennas, radiating or receiving electromagnetic noise. Follow these trace routing guidelines to keep EMI in check:

- Keep Traces Short and Direct: Longer traces increase the loop area, making them more susceptible to EMI. Route high-speed signals (above 50 MHz) as short and straight as possible to reduce radiation.

- Avoid Right-Angle Bends: Sharp 90-degree turns in traces can cause signal reflections and EMI radiation. Use 45-degree angles or curved traces to maintain signal integrity and minimize noise.

- Route Over Ground Planes: Ensure critical signal traces are routed over a ground plane to provide a consistent return path. This reduces the loop area and helps contain EMI. For differential pairs, maintain equal trace lengths to avoid common-mode noise, which can worsen during ESD events.

- Space Traces Appropriately: Maintain adequate spacing between traces to prevent crosstalk, especially for high-speed signals. A general rule of thumb is to keep spacing at least three times the trace width (3W rule) to minimize coupling.

Proper trace routing can significantly lower EMI risks. For instance, routing high-speed traces over a ground plane can reduce radiated emissions by 10-15 dB compared to routing over empty board areas.

3. Incorporate Transient Suppression for ESD Protection

Transient suppression is a direct way to mitigate the effects of ESD events, preventing high-voltage spikes from causing EMI or damaging components. Here are effective methods to integrate transient suppression into your PCB layout:

- Use Transient Voltage Suppression (TVS) Diodes: Place TVS diodes near sensitive input/output pins or connectors where ESD strikes are likely to occur, such as USB ports or power lines. These diodes clamp voltage spikes to safe levels, often below 30 volts, protecting downstream components. Choose a TVS diode with a clamping voltage slightly above your circuit’s operating voltage (e.g., a 5.6V TVS for a 5V system).

- Add ESD Suppressors Near Entry Points: Install ESD suppressors or spark gaps at board entry points to divert high-voltage transients to ground before they reach sensitive areas. For example, a spark gap designed on the PCB using closely spaced copper pads can arc over at 1,000 volts, safely dissipating ESD energy.

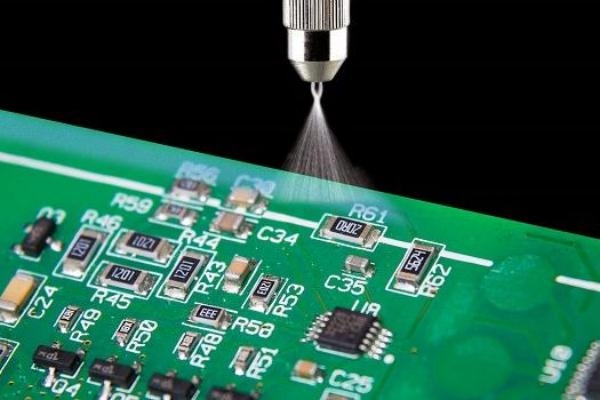

- Place Decoupling Capacitors Strategically: Position decoupling capacitors (e.g., 0.1 μF ceramic capacitors) close to IC power pins to filter out high-frequency noise from ESD events. Ensure the capacitor’s ground connection is as short as possible to maximize effectiveness.

Transient suppression components are vital for ESD protection. A well-placed TVS diode can reduce peak voltages from an 8,000-volt ESD strike to under 50 volts, drastically cutting EMI risks.

4. Shield Sensitive Areas to Block EMI

Shielding is another powerful technique to reduce EMI caused by ESD events. By enclosing sensitive components or areas of the PCB, you can prevent external noise from interfering with your design. Consider these shielding strategies:

- Use Copper Pour for Shielding: Surround critical components or high-speed traces with grounded copper pours on the top and bottom layers. Connect these pours to the ground plane with multiple vias to create a Faraday cage effect, blocking radiated EMI.

- Place Metal Shields Over Sensitive ICs: For extremely noise-sensitive components, such as RF modules, install metal cans or shields connected to ground. These shields can attenuate EMI by up to 30 dB, protecting against both external and internal interference.

- Isolate High-Noise Components: Physically separate components that generate significant noise (like switching regulators) from sensitive circuits. Use grounded copper barriers between these areas to contain EMI.

Shielding is especially useful in compact designs where components are densely packed, and EMI risks are higher. A grounded copper pour around a high-speed circuit can reduce noise pickup by a measurable margin, ensuring stable operation even during ESD events.

5. Design for Multi-Layer Boards When Possible

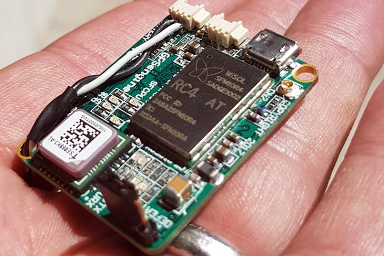

While single- or two-layer boards are cost-effective, multi-layer PCBs (four layers or more) offer superior EMI reduction and ESD protection. Here’s why:

- Dedicated Power and Ground Planes: Multi-layer boards allow for dedicated ground and power planes, providing low-impedance paths for currents and reducing noise coupling. A typical four-layer stack-up includes signal layers on the top and bottom, with ground and power planes in the middle.

- Better Signal Integrity: With internal planes, signal traces have consistent reference layers, minimizing loop areas and EMI radiation. This is critical for high-speed designs operating above 100 MHz.

- Enhanced Shielding: Internal ground planes act as natural shields, blocking EMI between layers and improving overall board performance during ESD strikes.

If budget allows, opting for a multi-layer design can reduce EMI issues by up to 25% compared to two-layer boards, especially in complex or high-speed applications.

Testing and Validation for EMI and ESD Performance

After implementing these PCB layout techniques, testing is essential to ensure your design meets EMI and ESD standards. Conduct the following tests to validate performance:

- ESD Testing: Use standards like IEC 61000-4-2 to simulate ESD events (e.g., 8 kV contact discharge) and check if your board withstands the stress without malfunction. Monitor for glitches or failures in critical circuits during testing.

- EMI Emissions Testing: Measure radiated and conducted emissions using a spectrum analyzer to ensure compliance with regulations like FCC Part 15 or CISPR standards. Identify frequency bands where EMI exceeds limits and adjust the layout if needed.

- Signal Integrity Analysis: Use an oscilloscope to verify that high-speed signals maintain integrity after ESD events. Look for overshoots or ringing that could indicate improper grounding or routing.

Regular testing helps catch design flaws early, saving time and cost in the long run. For instance, identifying a ground loop issue during EMI testing can prevent costly redesigns after production.

Conclusion: Building Resilient PCB Designs

Minimizing EMI from ESD events in PCB design requires a combination of careful planning and strategic layout techniques. By focusing on solid grounding, optimized trace routing, transient suppression, shielding, and multi-layer designs, you can significantly reduce the risks of interference and component damage. These practices not only enhance ESD protection but also ensure compliance with strict EMI regulations, resulting in reliable and high-performing electronics.

Implementing these techniques may take extra effort during the design phase, but the payoff is worth it. A well-designed PCB layout can withstand ESD strikes of up to 15 kV without inducing disruptive EMI, protecting your circuits and extending product lifespan. As you apply these strategies, remember to test and iterate on your designs to achieve the best results for your specific application.

With these actionable tips, you’re well-equipped to tackle EMI and ESD challenges in your next PCB project. Start incorporating these layout techniques today to build robust, interference-free designs that stand the test of time.

ALLPCB

ALLPCB