Overview

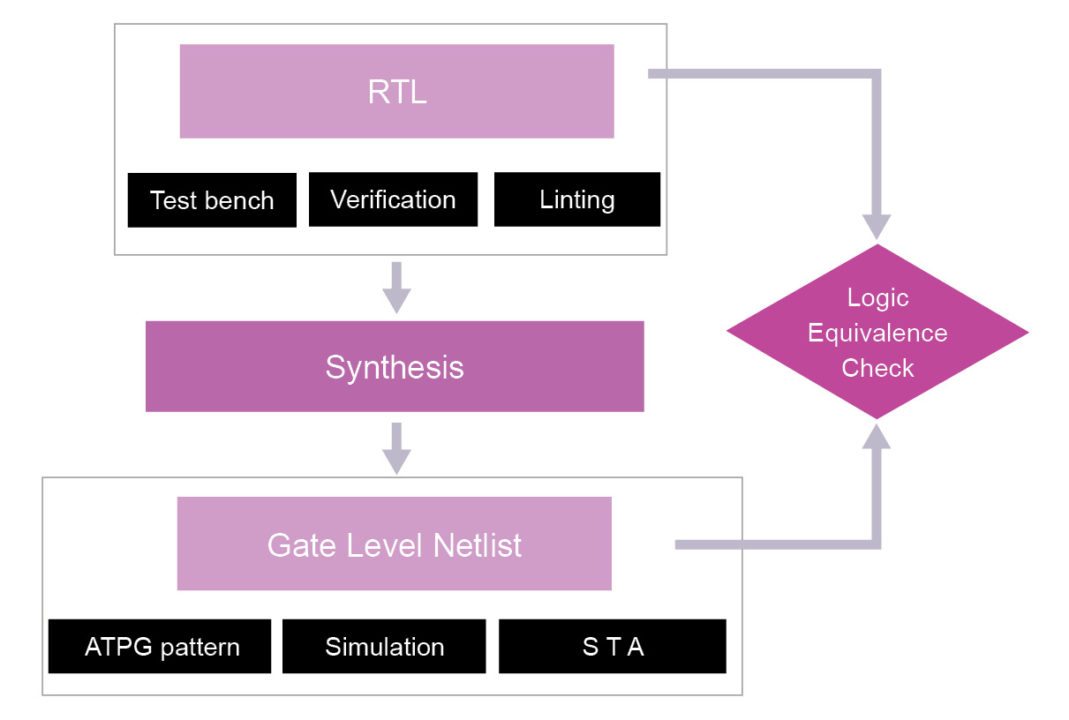

The boundary between front end and back end is defined at the gate-level netlist.

- Front end: logic design, RTL -> gate-level netlist.

- Back end: physical design, gate-level netlist -> physical layout.

- Synthesis: translate RTL code into a gate-level netlist.

A typical netlist file consists of cells, pins, ports, and nets.

Synthesis input: RTL code, technology library, constraints.

Synthesis output: gate-level netlist (for place and route), standard delay format (for timing simulation), and synthesis reports.

Functional Simulation

Functional simulation verifies the functional correctness of the RTL code without any timing information. This is also called pre-synthesis simulation. Common tools include Mentor ModelSim, Synopsys VCS, and Cadence NC-Verilog. After synthesis and place-and-route, post-synthesis simulation with timing is performed.

Synthesis

The goal of logic synthesis is to translate HDL code into a gate-level netlist. A common tool is Synopsys Design Compiler (DC). The resulting gate-level netlist is used for place and route.

Design for Test (DFT)

DFT adds structures to the design to enable testing. Common techniques include:

- Scan chain: for sequential circuits, it enables testing of flip-flops and combinational logic.

- MBIST (memory built-in self-test): tests on-chip memory resources such as ROM and RAM by inserting built-in self-test logic.

- Boundary scan: tests package I/O and chip-to-chip interconnects. Key components include the TAP controller and boundary scan chain; JTAG is a basic structure used in boundary scan designs.

ATPG (automatic test pattern generation) derives the stimulus and expected response sequences to be loaded into the scan chain; these sequences are called test vectors.

DFT implements the hardware structures; ATPG generates the test vectors.

Formal Verification

Formal verification is a form of verification that checks the synthesized netlist against the RTL design from a functional perspective. The common method is equivalence checking, which ensures synthesis did not change the original RTL behavior. A typical tool is Synopsys Formality.

Static Timing Analysis (STA)

STA (static timing analysis) verifies the synthesized netlist from a timing perspective, checking for violations such as setup and hold time violations. Note the difference: STA verifies timing, while formal verification verifies functional equivalence. A common STA tool is Synopsys PrimeTime.

ALLPCB

ALLPCB