In the fast-evolving world of 5G technology, designing printed circuit boards (PCBs) that support high-speed, low-latency, and wide-bandwidth networks is a critical challenge. One key aspect of this design is the via structure, which plays a major role in maintaining signal integrity. For engineers working on 5G PCB via design, minimizing inductance and signal loss is essential to ensure optimal performance. In this blog, we’ll dive deep into advanced via design techniques, focusing on microvia and buried via PCB structures, and provide actionable insights to help you tackle these challenges effectively.

Whether you’re dealing with via inductance issues or aiming to reduce signal loss via innovative layouts, this guide will walk you through the best practices and strategies for 5G network PCBs. Let’s explore how to optimize your designs for the future of connectivity.

Why Via Design Matters for 5G PCBs

5G networks operate at much higher frequencies than previous generations, often in the millimeter-wave range (24 GHz to 100 GHz). These high frequencies demand exceptional signal integrity, as even small imperfections in a PCB can lead to significant signal loss or interference. Vias, which are the small holes that connect different layers of a PCB, can introduce parasitic inductance and capacitance, disrupting signal flow if not designed carefully.

In 5G PCB via design, the goal is to minimize these parasitic effects to maintain signal quality. Poorly designed vias can act like tiny inductors, slowing down signal transitions and causing delays. They can also lead to signal loss via reflections or crosstalk, especially in high-density layouts. By focusing on advanced via structures like microvias and buried vias, engineers can address these issues and support the demands of next-generation networks.

Understanding Via Inductance and Signal Loss in 5G PCBs

Before diving into design techniques, it’s important to understand the problems of via inductance and signal loss. Inductance in a via occurs because the current flowing through it creates a magnetic field, which opposes changes in the current. This effect is more pronounced at high frequencies, where rapid signal changes are common in 5G systems. A typical via might have an inductance of 0.5 to 1.5 nH (nanohenries), which can significantly impact signal timing in a 5G circuit operating at 28 GHz.

Signal loss via other mechanisms, such as dielectric loss or impedance mismatches, also becomes a concern. When a signal passes through a via, any mismatch between the via’s impedance and the trace can cause reflections, reducing signal strength. For 5G applications, maintaining an impedance close to 50 ohms is often critical to avoid such losses.

Key Via Types for 5G PCB Design: Microvias and Buried Vias

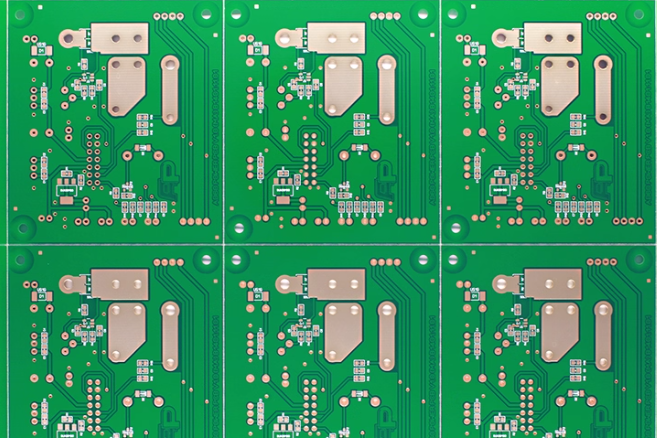

In modern 5G PCB designs, traditional through-hole vias are often replaced by advanced structures like microvias and buried vias. These via types are specifically suited for high-density interconnect (HDI) boards, which are common in 5G applications due to their compact size and multilayer construction.

Microvia PCB Structures

Microvias are small-diameter vias, typically less than 150 micrometers, created using laser drilling. They connect only adjacent layers in a PCB, reducing the overall via length and thus lowering inductance. For example, a microvia with a length of 0.1 mm might have an inductance of just 0.2 nH, compared to 1.0 nH for a longer through-hole via. This makes microvia PCB designs ideal for high-frequency 5G signals where minimizing inductance is critical.

Additionally, microvias allow for finer pitch components and tighter routing, which is essential for compact 5G devices like smartphones or IoT modules. However, they require precise manufacturing processes and can be more expensive than traditional vias.

Buried Via PCB Structures

Buried vias are connections between internal layers of a PCB that do not extend to the outer surfaces. Unlike through-hole vias, they don’t take up space on the top or bottom layers, allowing for cleaner layouts and reduced signal interference. In terms of signal loss via design, buried vias help by shortening signal paths and avoiding unnecessary stubs, which can cause reflections at high frequencies.

For 5G applications, buried vias are often used in multilayer boards to connect internal signal layers without affecting the outer shielding or ground planes. This helps maintain consistent impedance and reduces electromagnetic interference (EMI), a common issue in high-frequency designs.

Techniques to Minimize Inductance and Signal Loss in 5G PCB Vias

Now that we’ve covered the basics of via types, let’s explore specific techniques to optimize 5G PCB via design. These strategies focus on reducing via inductance and preventing signal loss via careful planning and innovative approaches.

1. Optimize Via Geometry and Placement

The physical dimensions of a via directly affect its inductance. A shorter and wider via will have lower inductance than a long, narrow one. For instance, reducing via length by 50% can decrease inductance by nearly the same proportion. In 5G PCB via design, aim to place vias as close as possible to the signal source or destination to minimize length. Additionally, using multiple vias in parallel for high-current paths can further reduce effective inductance.

Placement also matters for signal loss via impedance mismatches. Position vias away from critical signal traces or use ground vias nearby to stabilize return paths and reduce crosstalk. A common rule of thumb is to maintain a via-to-via spacing of at least twice the via diameter to avoid interference.

2. Leverage HDI and Microvia Technology

As mentioned earlier, microvia PCB structures are a go-to solution for 5G designs. Their small size and short length make them ideal for minimizing inductance. When designing with microvias, consider using a stacked or staggered configuration. Stacked microvias connect multiple layers directly, while staggered microvias offset connections to avoid stress points, both of which help maintain signal integrity at frequencies above 20 GHz.

HDI technology also allows for finer trace widths, often below 75 micrometers, which complements microvia designs by reducing overall signal path lengths and potential loss points.

3. Use Buried Vias for Cleaner Signal Paths

Incorporating buried via PCB designs can significantly reduce signal loss via stub effects. A stub is an unused portion of a via that acts like an antenna, reflecting signals and causing loss at high frequencies. By using buried vias, you eliminate these stubs since the via doesn’t extend beyond the connected layers. This is particularly useful in 5G designs where even small reflections can degrade performance at 28 GHz or higher.

4. Implement Proper Grounding and Return Paths

Grounding is critical in 5G PCB via design to manage via inductance and signal loss. Place ground vias near signal vias to provide a low-impedance return path for high-frequency currents. Without proper grounding, signals can loop through longer paths, increasing inductance and EMI. A typical guideline is to place a ground via within 0.5 mm of every signal via to ensure a stable return path.

Additionally, maintain continuous ground planes across layers to avoid interruptions that could force signals to detour, increasing loss. For multilayer 5G PCBs, dedicate entire layers to ground planes if possible.

5. Choose Low-Loss Materials

The material of your PCB impacts signal loss via dielectric properties. For 5G applications, select low-loss dielectric materials with a dissipation factor (Df) below 0.005 at high frequencies. Common choices include high-frequency laminates with a dielectric constant (Dk) around 3.0 to 3.5, which help maintain signal strength through vias and traces. These materials reduce energy loss as signals pass through the board, complementing advanced via designs.

Challenges in 5G PCB Via Design and How to Overcome Them

Designing vias for 5G PCBs comes with unique challenges due to the high frequencies and tight performance requirements. Here are some common hurdles and practical solutions to address them.

Challenge 1: Manufacturing Precision for Microvias

Microvias require precise laser drilling and plating processes, and even small defects can lead to signal loss via poor connections. To overcome this, work closely with your PCB fabricator to ensure they use reliable HDI manufacturing techniques. Specify aspect ratios (via depth to diameter) below 1:1 for microvias to avoid plating issues, as higher ratios can result in uneven copper deposition.

Challenge 2: Thermal Management with Buried Vias

Buried vias can trap heat in internal layers since they don’t reach the surface for dissipation. In 5G devices, where components generate significant heat, this can be problematic. Mitigate this by adding thermal vias near heat sources to conduct heat to outer layers, and use materials with high thermal conductivity for the PCB substrate.

Challenge 3: Cost vs. Performance Trade-Offs

Advanced via designs like microvias and buried vias increase manufacturing costs due to their complexity. Balance cost and performance by prioritizing these vias only in critical high-frequency signal paths. For less demanding sections of the PCB, standard through-hole vias might suffice, reducing overall expenses without compromising core functionality.

Best Practices for Simulating and Testing Via Designs

Simulation and testing are vital steps in ensuring your 5G PCB via design performs as expected. Use electromagnetic (EM) simulation tools to model via inductance and signal loss before fabrication. These tools can predict parasitic effects and help you tweak via dimensions or placement for optimal results. For instance, a simulation might reveal that a via with a 0.3 mm diameter causes a 10% signal reflection at 30 GHz, prompting a redesign.

After fabrication, perform signal integrity testing using a vector network analyzer (VNA) to measure impedance and loss through vias. Compare these results with your simulation data to validate the design. If discrepancies arise, adjust the layout or material choices accordingly in the next iteration.

Conclusion: Building the Future of 5G with Optimized Via Design

As 5G technology continues to transform connectivity, the importance of advanced via design in PCBs cannot be overstated. By focusing on minimizing via inductance and signal loss via techniques like microvia and buried via PCB structures, engineers can create boards that meet the stringent demands of high-frequency, low-latency networks. From optimizing via geometry to selecting low-loss materials, every detail counts in ensuring signal integrity and performance.

With the strategies and best practices outlined in this guide, you’re equipped to tackle the challenges of 5G PCB via design. Embrace these advanced techniques to build reliable, efficient boards that power the next generation of wireless communication. Let’s pave the way for faster, more connected systems with every via we design.