In the world of high-speed PCB design, maintaining signal integrity is a top priority. One technique that plays a significant role in achieving this is the use of via-in-pad technology. But what exactly is via-in-pad, and how does it impact signal integrity in high-speed PCB designs? In this blog, we’ll dive deep into via-in-pad signal integrity, explore its benefits for high-speed PCB design, and share actionable tips for reducing parasitic inductance and minimizing signal reflection. Whether you're an experienced engineer or just starting out, this guide will help you optimize your PCB layouts for better performance.

What Is Via-in-Pad and Why Does It Matter for Signal Integrity?

Via-in-pad refers to a PCB design technique where a via—a small hole that connects different layers of a circuit board—is placed directly within the pad of a component, such as a ball grid array (BGA) or other surface-mount devices. Unlike traditional vias placed outside the pad, this method saves space and shortens the signal path, which is critical for high-speed designs operating at frequencies above 1 GHz.

Signal integrity refers to the quality of an electrical signal as it travels through a PCB. Poor signal integrity can lead to data errors, noise, and performance issues in high-speed circuits. Via-in-pad helps by reducing the distance a signal must travel, minimizing delays, and cutting down on unwanted electrical effects like parasitic inductance and signal reflection. For engineers working on high-speed PCB design, adopting via-in-pad can be a game-changer in maintaining clean, reliable signals.

The Role of Via-in-Pad in High-Speed PCB Design

High-speed PCB design often involves signals traveling at speeds where even tiny delays or distortions can cause major problems. For instance, in applications like 5G communication, DDR memory interfaces, or high-performance computing, signal timing must be precise. A typical high-speed signal might operate at 10 Gbps, where a delay of just a few picoseconds can lead to bit errors.

Via-in-pad technology addresses these challenges by:

- Shortening Signal Paths: By placing the via directly under the component pad, the signal path is reduced, lowering the chance of timing issues.

- Supporting High-Density Designs: Modern devices often use BGAs with hundreds or thousands of pins in a small area. Via-in-pad allows for tighter layouts without sacrificing performance.

- Improving Routing Efficiency: It frees up space on outer layers, making it easier to route traces in complex designs.

However, via-in-pad isn’t without challenges. If not implemented correctly, it can introduce manufacturing issues or affect signal integrity. Let’s explore how to use this technique effectively while tackling potential pitfalls.

Signal Integrity Challenges in High-Speed PCB Design

Before diving into optimization strategies, it’s important to understand the common signal integrity challenges in high-speed PCB design. These issues often stem from parasitic effects that distort signals:

- Parasitic Inductance: Vias, traces, and other PCB elements can act like tiny inductors, storing energy and causing signal delays or overshoots. For a via with a length of 1.6 mm, inductance can be around 1-2 nH, enough to impact signals at 5 GHz or higher.

- Signal Reflection: When a signal encounters a change in impedance—such as at a via or connector—it can reflect back, causing noise and data errors. Reflections are especially problematic when impedance mismatches exceed 10% of the target value (e.g., 50 ohms).

- Crosstalk: High-speed signals can interfere with nearby traces, leading to unwanted noise coupling.

- Electromagnetic Interference (EMI): Poor design can radiate or pick up EMI, degrading performance.

Via-in-pad can help mitigate some of these issues, but only if paired with careful design practices. Let’s look at how to optimize via-in-pad for signal integrity.

Optimizing Via-in-Pad for Signal Integrity

Using via-in-pad effectively requires attention to detail during both design and manufacturing. Below are key strategies to ensure it enhances signal integrity in high-speed PCB designs.

1. Minimize Parasitic Inductance with Proper Via Design

Parasitic inductance is a major concern in high-speed designs because it slows down signal transitions and can cause ringing. To reduce parasitic inductance when using via-in-pad:

- Use Smaller Vias: Smaller via diameters (e.g., 0.2 mm or less) reduce inductance. Microvias, often used in high-density interconnect (HDI) designs, are ideal for this.

- Shorten Via Length: The shorter the via, the lower the inductance. For instance, a via spanning only two layers will have less inductance than one crossing six layers.

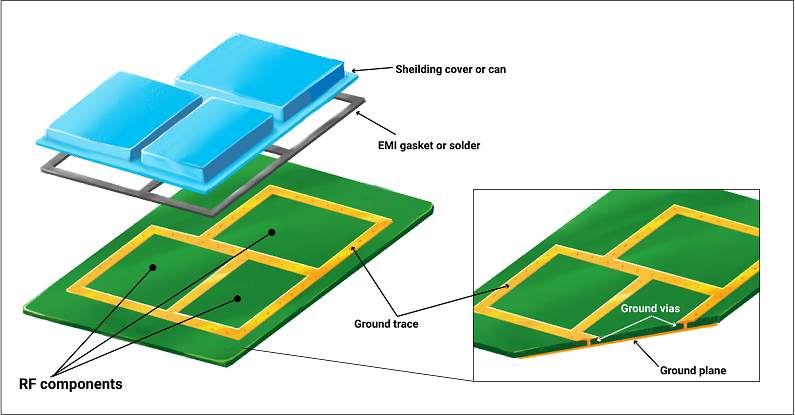

- Add Ground Vias Nearby: Placing ground vias close to signal vias creates a return path for current, reducing the loop area and thus lowering inductance. A common practice is to maintain a 1:1 ratio of ground to signal vias.

By focusing on these factors, engineers can cut via inductance by up to 50%, significantly improving performance at frequencies above 2 GHz.

2. Minimize Signal Reflection with Impedance Matching

Signal reflection occurs when there’s a mismatch in impedance along the signal path. Vias, including via-in-pad, can introduce impedance discontinuities if not designed properly. To minimize signal reflection:

- Match Via Impedance: Design vias to match the characteristic impedance of the trace, typically 50 ohms for high-speed signals. Tools like 3D field solvers can help calculate via impedance based on diameter, length, and surrounding materials.

- Use Back-Drilling: For through-hole vias, back-drilling removes unused via stubs that cause reflections. This is critical for signals operating at 10 Gbps or higher.

- Optimize Pad Size: Ensure the pad size for via-in-pad is balanced—not too large to increase capacitance, nor too small to affect manufacturing reliability.

Proper impedance matching can reduce reflection coefficients to below 0.1, ensuring cleaner signal transmission.

3. Leverage Ground Planes for Better Return Paths

A solid ground plane is essential for high-speed PCB design as it provides a low-inductance return path for signals. When using via-in-pad:

- Place Ground Planes Close to Signal Layers: This minimizes the loop area for return currents, reducing both inductance and EMI.

- Avoid Splitting Ground Planes: A continuous ground plane under signal traces and vias prevents impedance changes and signal disruptions.

- Stitch Vias Around Pads: Adding stitching vias (ground vias) around via-in-pad structures helps maintain a consistent reference plane, further improving signal integrity.

These practices ensure that return currents follow the shortest path, cutting down on noise and interference.

4. Consider Manufacturing Constraints

While via-in-pad offers clear benefits for signal integrity, it can complicate PCB fabrication if not planned properly. To avoid issues:

- Use Via Filling: Unfilled vias in pads can cause solder wicking during assembly, leading to poor connections. Epoxy or conductive filling ensures reliability.

- Work with Fabrication Limits: Check with your manufacturer for minimum via sizes and aspect ratios (via depth to diameter). Typical limits for microvias are a 1:1 aspect ratio for HDI boards.

- Plan for Thermal Management: Via-in-pad under components like BGAs can affect heat dissipation. Ensure thermal vias are included if needed.

Balancing design goals with manufacturing capabilities is key to a successful via-in-pad implementation.

Benefits and Drawbacks of Via-in-Pad in High-Speed PCB Design

Like any design technique, via-in-pad comes with trade-offs. Understanding these can help you decide when and how to use it.

Benefits

- Space Efficiency: Ideal for high-density layouts with fine-pitch components like 0.5 mm pitch BGAs.

- Improved Signal Integrity: Shorter signal paths and reduced inductance lead to cleaner signals at high frequencies.

- Better Routing Options: Frees up outer layer space for additional traces or components.

Drawbacks

- Manufacturing Complexity: Via-in-pad often requires advanced fabrication techniques like HDI, increasing costs.

- Potential Assembly Issues: Without proper filling, solder can flow into vias, causing defects.

- Design Constraints: Requires careful planning to avoid impedance mismatches or thermal issues.

Weighing these pros and cons will guide you in applying via-in-pad effectively for your specific project needs.

Practical Tips for Reducing Parasitic Inductance and Minimizing Signal Reflection

Beyond via-in-pad optimization, here are additional tips for tackling parasitic inductance and signal reflection in high-speed PCB design:

- Use Wider Traces: Wider traces (e.g., 8-10 mils for critical signals) lower inductance compared to narrow ones, though they increase capacitance—balance is key.

- Route Signals on Inner Layers: Inner layer routing near ground planes reduces EMI and inductance.

- Avoid Unnecessary Vias: Each via adds inductance (1-2 nH) and a potential reflection point. Use them only when needed.

- Simulate Designs: Use simulation tools to model signal behavior and identify issues like reflections or crosstalk before fabrication.

Implementing these strategies alongside via-in-pad can push your high-speed PCB design to the next level of performance.

Conclusion: Mastering Via-in-Pad for High-Speed PCB Success

Via-in-pad is a powerful technique for optimizing high-speed PCB designs, offering significant benefits for signal integrity by reducing parasitic inductance and minimizing signal reflection. By carefully designing vias, matching impedance, leveraging ground planes, and considering manufacturing constraints, engineers can harness the full potential of via-in-pad in their projects. Whether you’re working on cutting-edge 5G hardware or high-performance computing systems, these strategies will help ensure your signals remain clean and reliable, even at multi-GHz frequencies.

At ALLPCB, we’re committed to supporting your PCB design journey with resources and expertise to bring your ideas to life. By applying the tips and insights shared in this guide, you’ll be well-equipped to tackle the challenges of high-speed design and achieve outstanding results.

ALLPCB

ALLPCB