Designing a printed circuit board (PCB) involves balancing functionality, manufacturability, and reliability. One critical aspect of this process is understanding via spacing and clearance, especially when using blind and buried vias. If you're searching for clarity on PCB via spacing, blind via clearance, buried via clearance, and PCB design rules, you're in the right place. This guide offers a practical breakdown of these concepts, helping you navigate the complexities of modern PCB layouts with actionable tips and precise data.

In this comprehensive post, we'll dive deep into the importance of via spacing and clearance, explore the unique challenges of blind and buried vias, and provide clear guidelines to ensure your designs meet both performance and manufacturing standards. Whether you're a seasoned engineer or new to PCB design, this resource will equip you with the knowledge to create efficient and reliable boards.

What Are Vias and Why Do Spacing and Clearance Matter?

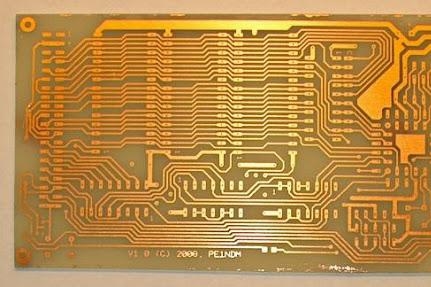

Vias are small holes in a PCB that allow electrical connections between different layers of the board. They are essential for routing signals and power in multi-layer designs. However, improper spacing and clearance around vias can lead to issues like signal interference, short circuits, or manufacturing defects. This is where PCB via spacing and clearance rules come into play, ensuring that your design operates as intended and can be produced without errors.

Spacing refers to the distance between vias or between a via and other components like traces or pads. Clearance is the minimum distance required to prevent electrical issues, such as arcing or crosstalk, between conductive elements. For standard through-hole vias, these rules are straightforward, but when dealing with blind and buried vias, the complexity increases due to their unique placement and manufacturing requirements.

Understanding Blind and Buried Vias

Before diving into spacing and clearance specifics, let's define blind and buried vias, as they differ from standard through-hole vias.

- Blind Vias: These connect an outer layer of the PCB to one or more inner layers but do not go through the entire board. They are often used to save space on the opposite side of the board, allowing for denser designs.

- Buried Vias: These are located entirely within the inner layers of the PCB and do not reach the outer surfaces. They are ideal for high-density interconnects (HDI) where space is limited, and multiple layer connections are needed.

Both types of vias are crucial for advanced PCB designs, especially in compact devices like smartphones or medical equipment. However, their placement and the associated blind via clearance and buried via clearance rules require extra attention due to manufacturing constraints and signal integrity concerns.

Key Challenges with Blind and Buried Via Spacing

Using blind and buried vias introduces several challenges that standard vias don't typically face. Here are the primary issues related to PCB via spacing when incorporating these advanced via types:

- Manufacturing Precision: Blind and buried vias require precise drilling and plating processes, often using laser technology for smaller diameters (down to 0.1 mm or 4 mils). Insufficient spacing can lead to drilling errors or weak connections.

- Signal Integrity: Close spacing between vias can cause crosstalk, especially in high-speed designs where signals operate at frequencies above 1 GHz. Maintaining proper clearance is critical to minimize interference.

- Thermal Management: Vias conduct heat as well as electricity. Inadequate spacing can lead to heat buildup, impacting the reliability of components nearby.

- Cost Implications: Tighter spacing and clearance requirements often increase manufacturing costs due to the need for advanced equipment and stricter quality control.

Understanding these challenges helps in setting realistic design parameters that balance performance with manufacturability.

PCB Design Rules for Via Spacing and Clearance

Adhering to PCB design rules is non-negotiable for creating functional and reliable boards. Below are general guidelines for via spacing and clearance, with specific considerations for blind and buried vias. These values are based on industry standards and typical manufacturing capabilities, though they may vary depending on your specific fabricator's constraints.

General Via Spacing Guidelines

- Minimum Via-to-Via Spacing: For standard through-hole vias, maintain at least 0.2 mm (8 mils) between vias to avoid drilling issues and ensure structural integrity.

- Via-to-Trace Clearance: Keep a minimum clearance of 0.15 mm (6 mils) between a via and adjacent traces to prevent short circuits.

- Via-to-Pad Clearance: Ensure at least 0.2 mm (8 mils) between a via and a component pad to avoid solder bridging during assembly.

Specific Rules for Blind Via Clearance

Blind vias, due to their partial depth, have unique clearance requirements to ensure proper drilling and plating:

- Blind Via-to-Blind Via Spacing: Maintain a minimum of 0.25 mm (10 mils) to prevent overlap during laser drilling, which can compromise the via's integrity.

- Blind Via-to-Trace Clearance: A clearance of at least 0.2 mm (8 mils) is recommended to avoid electrical interference, especially in high-speed designs with impedance values around 50 ohms.

- Aspect Ratio Consideration: Blind vias often have a lower aspect ratio (depth-to-diameter), typically 1:1 or less, to ensure reliable plating. This impacts how close they can be placed to other features.

Specific Rules for Buried Via Clearance

Buried vias, hidden within inner layers, require even stricter rules due to their inaccessibility for inspection or repair:

- Buried Via-to-Buried Via Spacing: Keep a minimum spacing of 0.3 mm (12 mils) to account for alignment challenges during lamination and drilling of inner layers.

- Buried Via-to-Inner Layer Trace Clearance: Ensure a clearance of 0.25 mm (10 mils) to prevent signal crosstalk and maintain impedance control, particularly for differential pairs with typical impedance of 100 ohms.

- Layer Stack-Up Constraints: Buried vias must align with the PCB stack-up design, often requiring tighter tolerances to avoid misalignment with other layers.

These values are starting points. Always consult your PCB manufacturer for their specific capabilities, as advanced processes might allow tighter spacing, or conversely, require more conservative clearances.

Practical Tips for Implementing Via Spacing and Clearance

Now that we've covered the basic rules, let's explore practical strategies to apply these guidelines effectively in your designs. These tips will help ensure your PCB layout is both functional and manufacturable.

1. Use Design Software with DRC Features

Most PCB design tools include Design Rule Check (DRC) features that automatically flag spacing and clearance violations. Set up your DRC parameters based on the guidelines above or your manufacturer's specifications. For instance, if you're designing for high-speed signals at 2.5 GHz, ensure the software accounts for controlled impedance and via spacing to minimize signal loss.

2. Prioritize Signal Integrity in High-Density Designs

In HDI designs with blind and buried vias, signal integrity is paramount. Place vias strategically to avoid creating stubs that can cause signal reflection. For example, in a 10-layer board, position buried vias away from critical signal paths on adjacent layers to reduce crosstalk by at least 3 dB.

3. Collaborate with Your Manufacturer Early

Manufacturing capabilities vary widely. Some fabricators can handle blind via diameters as small as 0.1 mm with a 0.2 mm spacing, while others may require 0.3 mm or more. Share your design intent early to align your via spacing and clearance with their process limits, avoiding costly redesigns.

4. Test and Validate Your Design

Before finalizing your layout, simulate signal performance using tools that model electromagnetic interference (EMI) and crosstalk. Validate that your blind via clearance and buried via clearance meet the required standards for your application, especially if dealing with high-frequency signals above 500 MHz.

Common Mistakes to Avoid with Blind and Buried Vias

Even with the best intentions, errors in via spacing and clearance can slip through. Here are some pitfalls to watch out for:

- Ignoring Aspect Ratio Limits: Blind vias with an aspect ratio exceeding 1:1 can lead to plating issues, causing open circuits. Stick to manufacturer-recommended ratios.

- Overcrowding Vias: Placing too many blind or buried vias in a small area can weaken the PCB structure and increase the risk of shorts. Spread them out wherever possible.

- Neglecting Thermal Vias: If using vias for heat dissipation, ensure adequate spacing to avoid creating thermal hotspots that could affect nearby components.

- Misaligning Stack-Up Layers: For buried vias, improper layer alignment during design can result in failed connections. Double-check your stack-up plan.

How Via Spacing Impacts Manufacturing Costs

It's important to recognize that tighter PCB via spacing and clearance requirements often translate to higher production costs. Here's why:

- Advanced Drilling Techniques: Blind and buried vias often require laser drilling, which is more expensive than mechanical drilling used for through-hole vias.

- Quality Control: Smaller clearances demand stricter inspection processes, such as X-ray testing, to detect defects in buried vias.

- Material Usage: HDI designs with multiple via types may require specialized materials or additional layers, increasing overall expenses.

Balancing design complexity with cost is key. Opt for the tightest spacing only when necessary for performance, and consider relaxing constraints where possible without compromising functionality.

Conclusion: Mastering Via Spacing for Better PCB Designs

Navigating the intricacies of PCB via spacing, blind via clearance, and buried via clearance is a critical skill for any PCB designer. By adhering to well-defined PCB design rules and understanding the unique requirements of blind and buried vias, you can create layouts that are both high-performing and manufacturable. Start with the guidelines provided—such as maintaining a 0.25 mm spacing for blind vias and 0.3 mm for buried vias—and adjust based on your manufacturer's capabilities and project needs.

Remember to leverage design tools, prioritize signal integrity, and collaborate with your fabricator to avoid common pitfalls. With these strategies, you'll be well-equipped to tackle even the most complex PCB designs, ensuring reliability and efficiency in every project.

ALLPCB

ALLPCB