Introduction

This article summarizes design and implementation considerations for Xilinx Zynq-7000 embedded systems.

Zynq Concept and Design Tools

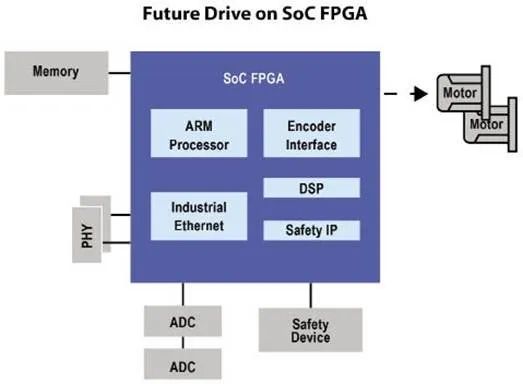

The Zynq family integrates two complementary execution models: serial execution on an ARM processor and parallel execution on an FPGA fabric. This heterogeneous approach is aimed at high-performance data processing tasks such as big data and artificial intelligence algorithms. Modern design tools, notably Vivado HLS, emphasize system-level modeling. Using HLS, developers can write C code and have tools generate corresponding HDL implementations for programmable logic.

Trends in Heterogeneous System Design

As heterogeneous architectures and system-on-chip technologies evolve, co-design, co-simulation, and co-debugging become essential skills for embedded system developers. Designers need competency in both software and hardware, which contrasts with traditional separated software/hardware workflows. Advances in semiconductor technology have driven electronic systems from board-level designs to chip-level integration, supporting improvements in miniaturization, power consumption, and reliability.

1. All-Programmable System-on-Chip Basics

Based on conventional FPGA technology (Field Programmable Gate Array, FPGA), all-programmable system-on-chip (All Programmable SoC, AP SoC) platforms integrate dedicated processor cores and programmable logic resources on a single chip, creating a unified design platform.

Comparison: SoC, CPU, MCU

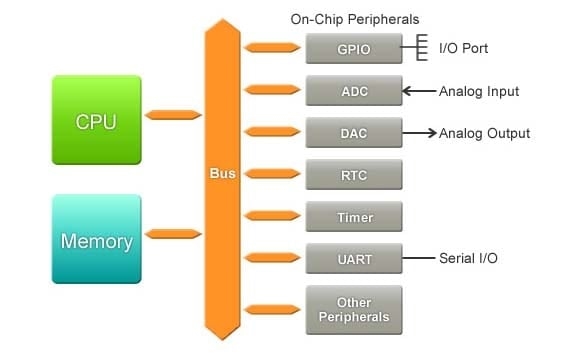

- SoC: Can integrate multiple high-performance processor cores, memory blocks, IO resources and peripherals. May include GPU, DSP, audio/video decoders and can run various operating systems. Targeted at advanced applications such as smartphones and tablets.

- CPU: Single processor core that requires external memory and peripherals; widely used across many applications.

- MCU: Typically a single core with integrated memory, IO and peripherals, commonly used in embedded and industrial control applications.

Background of AP SoC

Design flows for all-programmable platforms shift from HDL-centered hardware logic design to C-language-centered functional descriptions. This enables describing embedded system structure in C while using HDL to describe hardware implementations, supporting true software-hardware co-design for AP SoC-based systems.

Hardware Acceleration Advantage

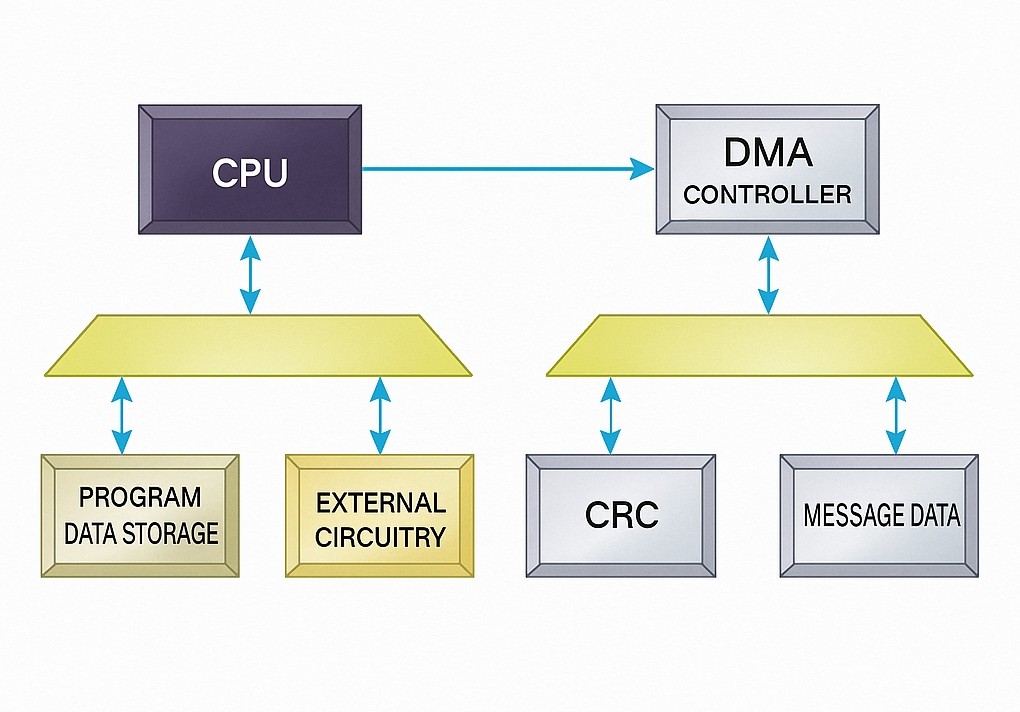

Designers can trade off between hardware and software implementations to meet performance and cost targets. When a software algorithm becomes a system performance bottleneck, it can be implemented in hardware as a custom coprocessor in the programmable logic. Such coprocessors connect to the ARM Cortex-A9 processor in the processing system via AMBA interfaces. High-level synthesis tools allow converting software bottlenecks into hardware implementations efficiently.

2. Processor Types in All-Programmable SoC

Processors in all-programmable SoC platforms are classified as hard-core or soft-core.

Hard-core processors: Earlier Xilinx devices integrated IBM PowerPC hard cores in Virtex-5 series. The Zynq-7000 series integrates a dual-core ARM Cortex-A9 hard core.

Soft-core processors: When high processor performance is not required, a dedicated silicon area is not necessary. Instead, a processor can be implemented using FPGA resources such as LUT RAM, flip-flops and interconnect. Soft cores are described in HDL or as netlists and must be synthesized before use.

3. Zynq-7000 SoC Features and Architecture

The dual-core ARM Cortex-A9 multicore CPU serves as the heart of the processing system (PS). It includes on-chip memory, external memory interfaces and a range of peripherals. Compared with traditional FPGA and SoC approaches, Zynq-7000 delivers the flexibility and scalability of FPGA fabric while offering performance, power characteristics and ease of use comparable to dedicated integrated circuits.

The architecture facilitates mapping custom logic and software to the programmable logic (PL) and processing system (PS), enabling differentiated system functionality. Unlike FPGA-only workflows, Zynq-7000 boots the PS first, which allows software running on the PS to initialize the system and configure the PL. PL configuration can be part of the boot sequence or performed later, and the platform supports full reconfiguration or partial reconfiguration (PR) for dynamic modification of PL regions.

This overview concludes here. Subsequent material will cover PS and PL composition, interconnect structures, power and pin considerations, and MIO to EMIO connectivity.

ALLPCB

ALLPCB