In the world of electronics, crystal oscillators are the heartbeat of many devices, providing precise timing signals for microcontrollers, communication systems, and more. However, achieving optimal stability in high-density PCB designs can be a challenge. How do you ensure crystal oscillator stability in PCB layouts while managing electromagnetic interference (EMI), grounding, and impedance issues? The key lies in careful design practices, including proper layout, grounding techniques, and impedance matching.

In this comprehensive guide, we’ll explore the critical factors for maintaining crystal oscillator stability in PCB designs. From crystal oscillator grounding techniques to EMI reduction and layout best practices, we’ll cover actionable tips to help engineers design robust, high-performance boards. Let’s dive into the details of creating stable and reliable timing circuits in compact, high-density environments.

Understanding Crystal Oscillators and Their Role in PCB Designs

Crystal oscillators are essential components in electronic circuits, generating precise frequencies by vibrating a quartz crystal at a specific resonant frequency. They’re widely used in microprocessors, RF systems, and digital circuits to ensure accurate timing. However, in high-density PCB designs, where components are packed tightly together, maintaining crystal oscillator stability in PCB layouts becomes increasingly complex due to noise, interference, and parasitic effects.

Stability refers to the oscillator’s ability to maintain a consistent frequency over time and under varying conditions like temperature changes or mechanical stress. Poor stability can lead to timing errors, signal jitter, or complete system failure. With the right design approach, you can minimize these risks and ensure reliable performance.

Challenges of Crystal Oscillator Stability in High-Density PCBs

High-density PCB designs present unique challenges for maintaining crystal oscillator stability in PCB environments. Here are some common issues engineers face:

- Parasitic Capacitance and Inductance: Close proximity of components and traces can introduce unwanted capacitance and inductance, shifting the oscillator’s resonant frequency.

- Electromagnetic Interference (EMI): High-frequency signals from nearby components can couple with the oscillator circuit, causing noise and instability.

- Thermal Effects: Heat generated by densely packed components can alter the crystal’s frequency, especially in compact designs with limited airflow.

- Mechanical Stress: Vibrations or physical shocks in high-density boards can affect the crystal’s performance, leading to phase noise.

Addressing these challenges requires a combination of proper component selection, layout optimization, and noise mitigation strategies. Let’s explore the best practices for achieving stability.

Crystal Oscillator Layout Best Practices for High-Density Designs

The physical layout of a crystal oscillator on a PCB plays a critical role in its performance. Follow these crystal oscillator layout best practices to minimize noise and ensure stability:

- Place the Crystal Close to the Oscillator Pins: Position the crystal as close as possible to the oscillator input and output pins of the microcontroller or IC. This reduces trace length, minimizing parasitic capacitance and the risk of interference. Ideally, keep traces under 10 mm in length.

- Minimize Trace Loops: Avoid creating loops in the signal traces connected to the crystal. Loops act as antennas, picking up EMI and introducing noise. Use straight, short traces instead.

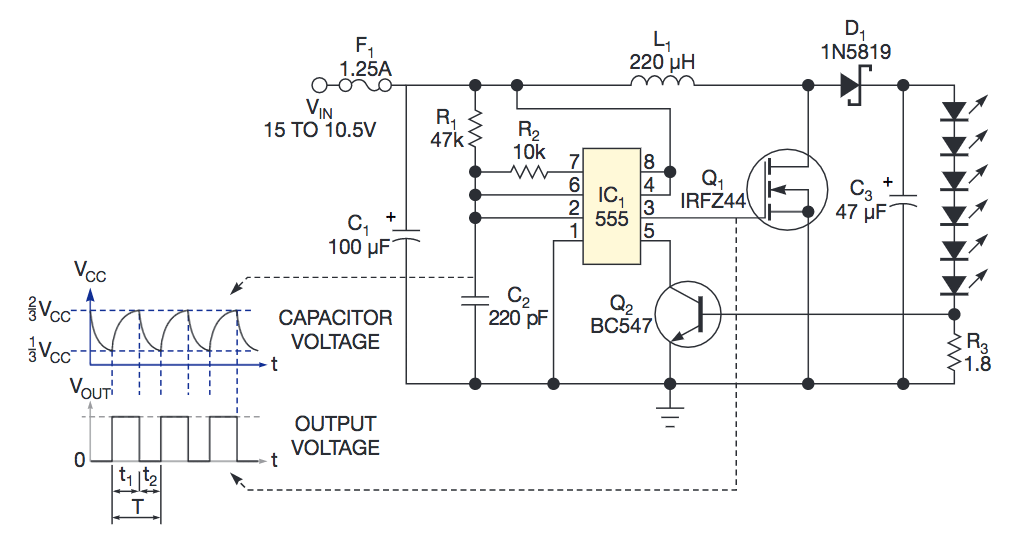

- Isolate from High-Frequency Components: Keep the crystal and its associated circuitry away from high-frequency components like switching regulators or RF transceivers. If isolation isn’t possible, use shielding techniques to block interference.

- Use Symmetrical Traces for Load Capacitors: Place load capacitors symmetrically on either side of the crystal to balance the circuit. Ensure the capacitors are also close to the crystal to avoid long traces that could introduce noise.

By adhering to these layout guidelines, you can significantly improve crystal oscillator stability in PCB designs, even in tightly packed boards.

Crystal Oscillator Grounding Techniques for Stability

Grounding is one of the most critical aspects of maintaining crystal oscillator stability in PCB designs. Poor grounding can lead to noise coupling and frequency drift. Here are some proven crystal oscillator grounding techniques to follow:

- Dedicated Ground Plane: Use a solid, uninterrupted ground plane beneath the crystal oscillator circuit. This provides a low-impedance return path for signals and reduces EMI. Avoid splitting the ground plane under the oscillator area, as splits can create noise.

- Ground Vias for Capacitors: Connect the ground pins of load capacitors directly to the ground plane using vias. This minimizes inductance in the ground path, ensuring cleaner signals. Place vias as close as possible to the capacitor pads.

- Separate Analog and Digital Grounds: If your PCB includes both analog and digital circuits, separate their ground planes to prevent digital noise from affecting the oscillator. Connect the grounds at a single point, often near the power supply, to avoid ground loops.

- Guard Ring for Isolation: Surround the crystal oscillator circuit with a grounded guard ring. This ring acts as a barrier, reducing EMI from nearby components. Connect the guard ring to the ground plane with multiple vias for maximum effectiveness.

Effective grounding not only enhances stability but also plays a vital role in crystal oscillator EMI reduction. A well-designed ground plane can act as a shield, protecting the oscillator from external noise sources.

Crystal Oscillator EMI Reduction Strategies

Electromagnetic interference (EMI) is a major threat to crystal oscillator stability in PCB designs, especially in high-density layouts where components are closely spaced. Implementing crystal oscillator EMI reduction techniques is essential for reliable operation. Here’s how to minimize EMI:

- Shielding: Use metal shields or cans over the crystal oscillator to block external electromagnetic fields. Ensure the shield is properly grounded to the PCB’s ground plane.

- Filter High-Frequency Noise: Add bypass capacitors (typically 0.1 μF to 1 μF) near the power supply pins of the oscillator circuit. These capacitors filter out high-frequency noise that could interfere with the crystal’s operation.

- Reduce Crosstalk: Route oscillator traces away from high-speed digital lines or power traces. If crossing is unavoidable, ensure traces cross at a 90-degree angle to minimize coupling.

- Control Signal Rise Times: If the oscillator drives other components, use series resistors (e.g., 22 ohms to 33 ohms) to slow down signal rise times. Faster rise times generate more EMI, so controlling them can reduce interference.

By focusing on crystal oscillator EMI reduction, you can prevent frequency jitter and maintain a stable timing signal, even in noisy environments.

Crystal Oscillator Impedance Matching for Optimal Performance

Impedance matching is often overlooked but is crucial for achieving crystal oscillator stability in PCB designs. Proper crystal oscillator impedance matching ensures maximum power transfer and minimizes signal reflections that could disrupt the oscillator’s frequency. Here’s how to approach it:

- Select the Right Load Capacitors: Crystal oscillators require specific load capacitance to operate at their designed frequency. Check the crystal’s datasheet for the recommended load capacitance (often 12 pF to 20 pF). Mismatched capacitors can shift the frequency, leading to instability. For example, if the crystal specifies a load capacitance of 18 pF, ensure the total capacitance, including PCB parasitics (typically 2-5 pF), matches this value.

- Match Trace Impedance: Design the traces connected to the crystal to match the characteristic impedance of the system. For most low-frequency crystals (below 30 MHz), this isn’t a major concern, but for higher frequencies, controlled impedance traces (e.g., 50 ohms) may be necessary to prevent reflections.

- Minimize Parasitic Effects: Long traces or improper routing can add parasitic capacitance, altering the effective load on the crystal. Keep traces short and avoid routing them over splits in the ground plane to maintain consistent impedance.

Accurate crystal oscillator impedance matching ensures the oscillator starts reliably and maintains its frequency without drift, even under varying load conditions.

Additional Tips for Enhancing Crystal Oscillator Stability

Beyond layout, grounding, EMI reduction, and impedance matching, here are a few more tips to boost crystal oscillator stability in PCB designs:

- Choose the Right Crystal: Select a crystal with a low frequency tolerance (measured in parts per million, or ppm). For critical applications, opt for crystals with tolerances of ±10 ppm or better to ensure minimal frequency drift.

- Account for Temperature Effects: Use temperature-compensated crystal oscillators (TCXOs) if your design operates in environments with wide temperature swings. TCXOs can maintain stability within ±0.5 ppm over a range of -40°C to 85°C.

- Simulate Your Design: Use PCB design software to simulate the oscillator circuit before manufacturing. Simulation can help identify potential issues like parasitic capacitance or EMI coupling early in the design process.

- Test Under Real Conditions: After fabrication, test the PCB under real-world conditions, including temperature variations and mechanical stress, to verify the oscillator’s stability.

These steps can help fine-tune your design and address any overlooked factors affecting stability.

Conclusion: Building Stable High-Density PCB Designs with Crystal Oscillators

Achieving crystal oscillator stability in PCB designs, especially in high-density layouts, requires careful attention to detail. By following crystal oscillator layout best practices, implementing effective crystal oscillator grounding techniques, focusing on crystal oscillator EMI reduction, and ensuring proper crystal oscillator impedance matching, you can create reliable, high-performance timing circuits.

Start with a well-thought-out layout, keeping traces short and components isolated from noise sources. Build a solid grounding strategy with dedicated planes and vias to minimize interference. Use shielding and filtering to tackle EMI, and match impedance to prevent frequency drift. With these practices in place, your high-density PCB designs will deliver consistent, stable performance for any application.

Designing PCBs with crystal oscillators doesn’t have to be daunting. Armed with these actionable tips, you’re ready to tackle the challenges of high-density environments and ensure your timing circuits perform flawlessly.

ALLPCB

ALLPCB